总览

最简单的时序电路是双稳态电路时序逻辑构件:锁存器(Latches)和触发器(Flip-Flops),锁存器和触发器都是具有存储功能的双稳态元器件。

在锁存器或触发器中,对状态值的描述定义如下:将 $Q=0$、 $\overline Q =1$ 这种状态定义为0态,表示存储的值为0;将 $Q=1$、 $\overline Q =0$ 这种状态称为1态,表示存储的值为1。

在逻辑表达式中,一般用 ${Q^n}$ 代表存储电路的当前状态(现态),用 ${Q^{n+1}}$ 代表存储电路的下一个状态。

在状态图中,通常斜线左边表示的是输入信号(状态转换条件),斜线右边表示的是输出信号。

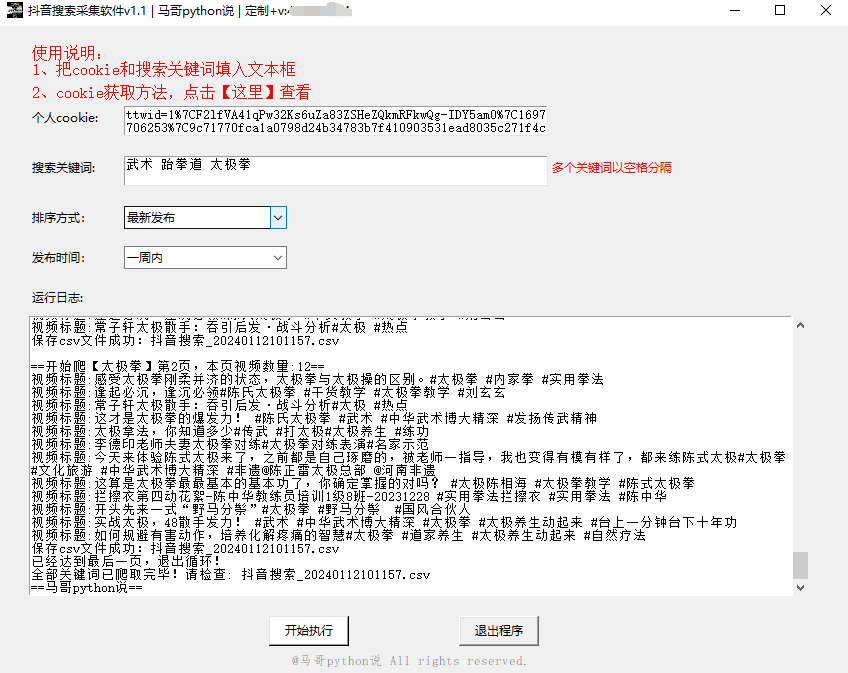

书上介绍的锁存器和触发器粗略的总结如下:

时序电路的分类

1. 按触发器的时钟脉冲控制方式分类

- 同步时序电路 :存储电路中所有的触发器状态的改变都是在同一个时钟脉冲(Clk)控制下同时发生。

- 异步时序电路 :存储电路中的触发器由两个或两个以上的 Clk 控制或没有 Clk 控制。

2. 按输出和输入的关系分类

- Mealy型时序电路:输出不但取决于当前的输入,还取决于当前(存储电路)的状态。$Y = F\left[ {X,{Q^n}} \right]$

- Moore型时序电路:输出仅与当前(存储电路)的状态有关。$Y = F\left[ {{Q^n}} \right]$

时序电路的特点

1. 逻辑功能上的特点

- 任意时刻电路的稳定输出,不仅取决于该时刻各个输入变量的取值,还取决于电路原来的状态。即:与以前的输入有关。

2. 电路结构上的特点

- 通常包含组合电路和存储电路(必不可少)由具有记忆功能的锁存器或触发器构成。

- 存储电路的输出状态必须反馈到组合电路的输入端,与输入信号一起,共同决定组合电路的输出。

锁存器

锁存器是电平敏感(输入信号直接控制着输出的状态)的存储元件,存储状态随着输入信号的高低电平变化而变化。

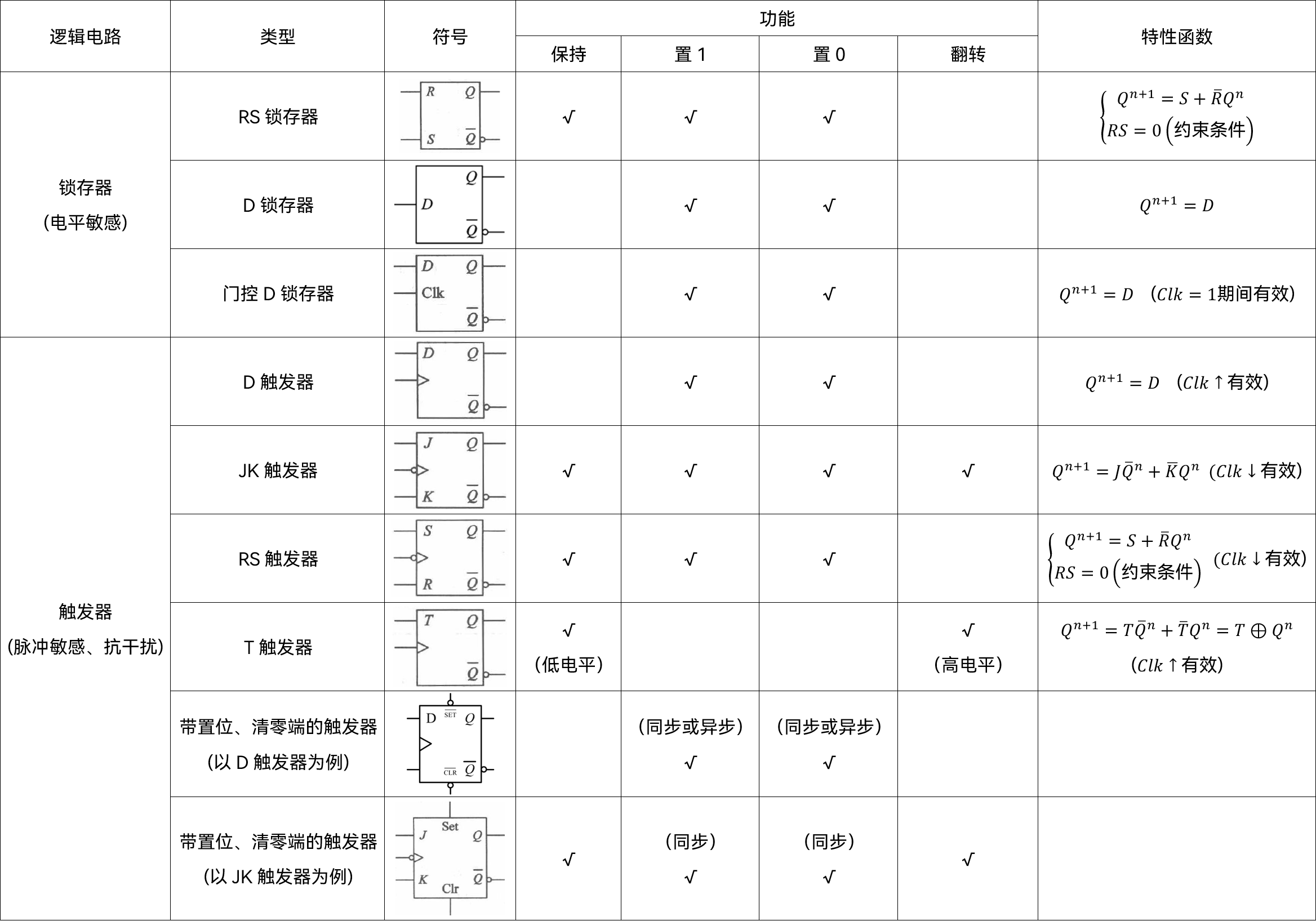

1. 基本RS锁存器

基本RS锁存器(Basic RS latches)的电路比较简单,它是组成各种功能更为完善的锁存器及触发器的基本单元;其输入信号直接控制着输出的状态(称为电平敏感),根据输入信号的不同,基本RS锁存器具有保持、置1、置0功能;输入信号R、S之间有约束。

RS锁存器的基本结构:

基本RS锁存器有两个输入端 $R$ 和 $S$

- $R (Reset)$ 为置0端,或称复位端。

- $S (set)$ 为置1端,或称置位端。

两个输出端 $Q$ 和 $\overline Q $ 为互补输出端,它们输出的状态刚好相反。

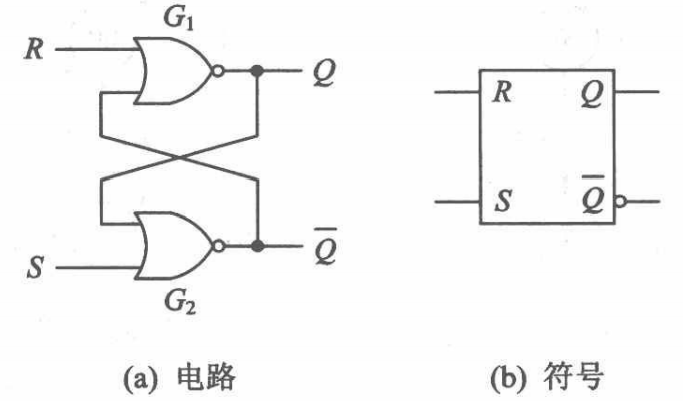

特性表如下:

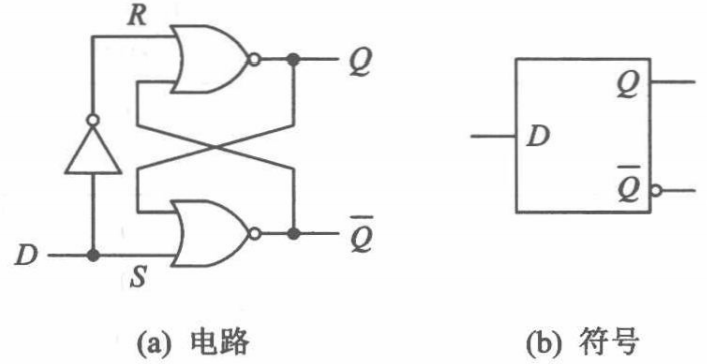

2. D锁存器

D锁存器(The D latches)为电平直接控制,不存在RS触发器的约束问题;D锁存器具有置0及置1功能。

D锁存器的基本结构:

仅有一个输入端D,D为输入信号。

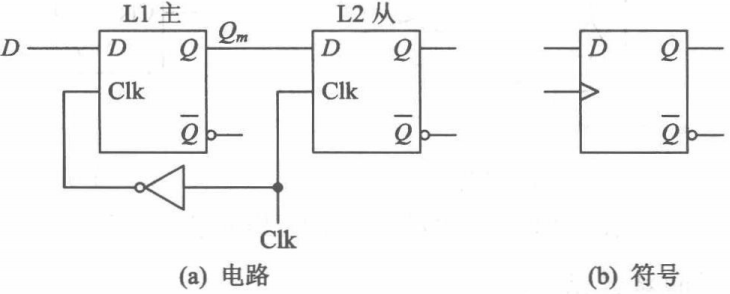

特性表如下:

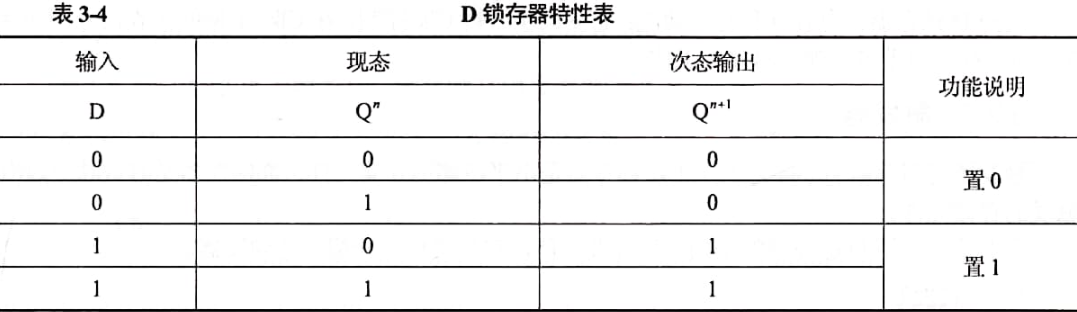

3. 门控D锁存器

门控D锁存器(The clocked D latch)具有置0和置1功能;它受同步时钟Clk控制,在Clk=1期间接收信号,Clk=0期间锁存,便于多个锁存器同步工作。

门控D锁存器的基本结构:

(1)当 $Clk=0$ 时,$R=S=0$ ,此时锁存器的状态不会改变,即 ${Q^{n + 1}} = {Q^n}$。

(2)当 $Clk=1$ 时,由输入信号 $D$ 控制锁存器状态,即 ${Q^{n + 1}} = {D}$。

触发器

触发器是时钟脉冲边沿触发的存储元件,存储状态仅在时钟脉冲边沿可能发生改变。

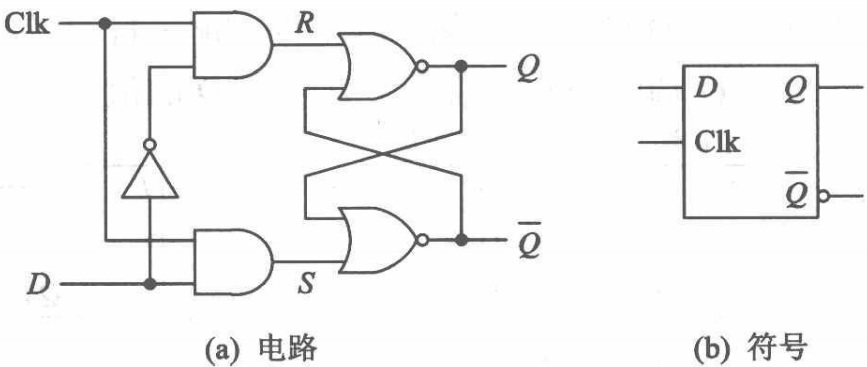

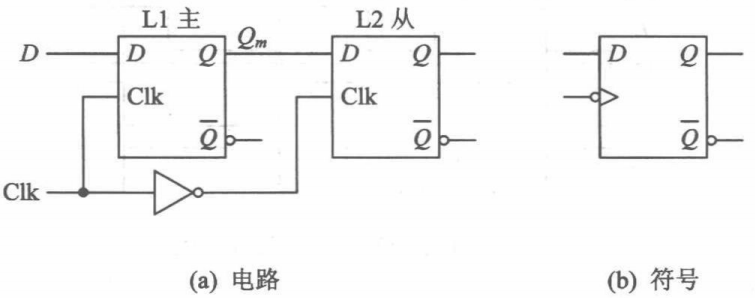

1. D触发器

D触发器具有置0及置1功能;时钟脉冲边沿控制,便于多个触发器同步工作,抗干扰能力强。

由于D信号只在时钟脉冲Clk的边沿复制到Q端,故这类触发器又被称为主从触发器(master-slave flip-flop)或边沿触发器(edge flip-flop)。逻辑符号中的三角表示触发器使用时钟边沿触发,上图(b)中的符号所表示的边沿为时钟 Clk 的上升沿(rising edge)。若符号中的三角外有一圆圈,表示的是下降沿(falling edge)触发,见下图(b)。

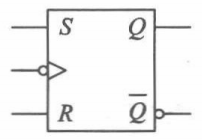

特性表:

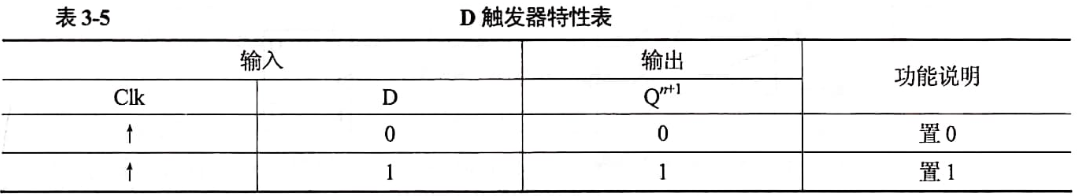

2. JK触发器

JK触发器具有保持、置0、置1、翻转功能;时钟脉冲边沿控制,抗干扰能力强。

特性表如下:

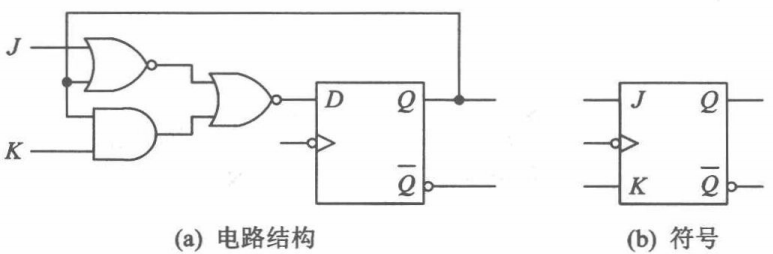

3. RS触发器

RS触发器具有保持、置0、置1功能;时钟脉冲边沿控制,抗干扰能力强;R、S之间有约束。

特性表与RS锁存器相同。

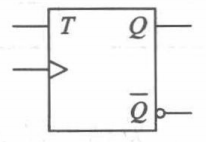

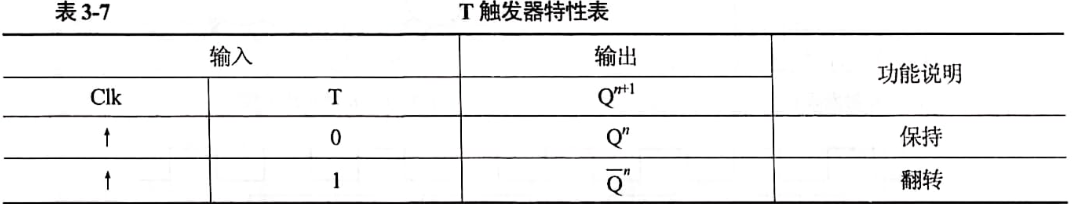

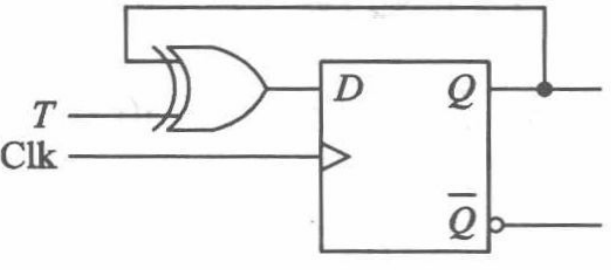

4. T触发器

T触发器具有保持、翻转功能;时钟脉冲边沿控制,抗干扰能力强。

特性表如下:

5. 带置位、清零端的触发器

根据置位或者清零是否受时钟信号Clk约束,可以分为:

异步方式(Asynchronous mode):当置位或清零信号一产生就立刻进行置位或清零操作。

同步方式(Synchronization mode):当置位或清零信号产生后,还要等待时钟脉冲信号的有效边沿到来才进行置位或清零操作

-

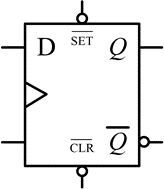

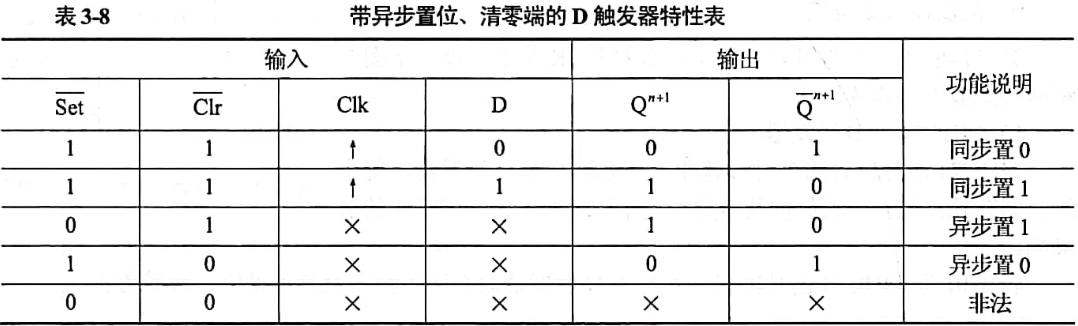

带异步置位、清零端的D触发器

逻辑符号中增加了异步置位端 $\overline {Set} $以及异步清零端 $\overline {Clr} $

特性表如下:

-

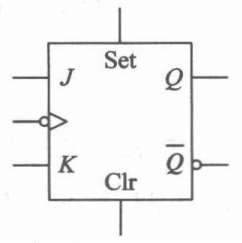

带同步置位、清零端的JK触发器

逻辑符号中 $\overline {Set} $以及 $\overline {Clr} $ 分别为同步置位及清零端,均为高电平有效。

特性表如下:

触发器逻辑功能的转换

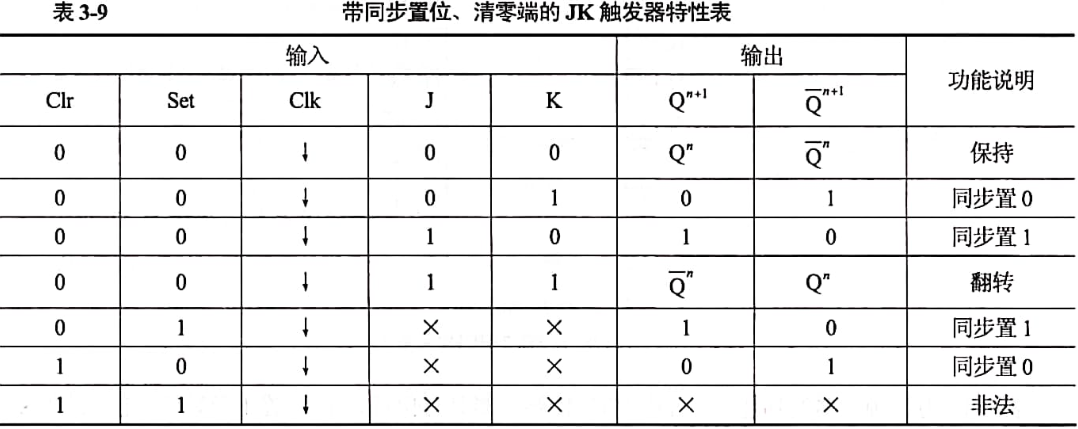

1. D触发器构造

-

RS触发器

由RS触发器的特性函数得,转换逻辑为 $D = S + \overline R {Q^n}$

-

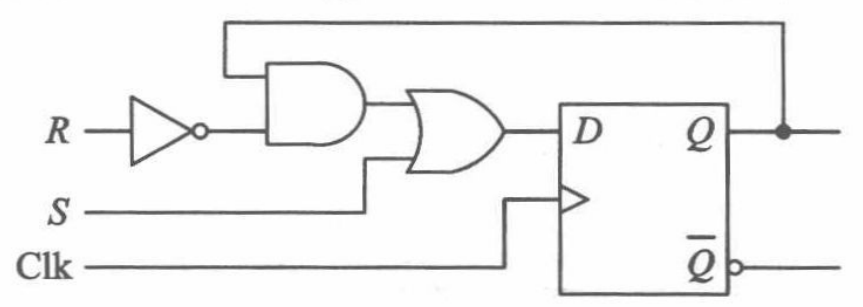

T触发器

由T触发器的特性函数得,转换逻辑为 $D = T \oplus {Q^n}$

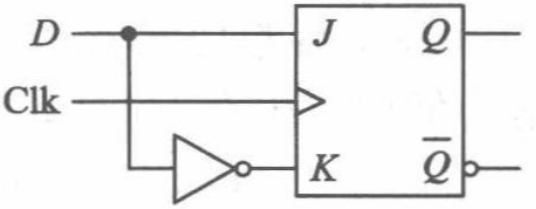

2. JK触发器构造

-

RS触发器

S信号从J端接入,R信号从K端接入即可。

-

T触发器

由T触发器的特性函数得,转换逻辑为 $J=K=T$

-

D触发器

由D触发器的特性函数得,转换逻辑为 $J=D$,$K = \overline D $