一、基本及常用逻辑运算

见下表

二、组合逻辑电路

1. 组合电路的特点

逻辑功能特点:电路在任何时刻的输出状态只取决于该时刻的输入状态,而与原来的状态无关。

电路结构特点:输出、输入之间没有反馈延迟电路;不包含记忆性元件(触发器),仅由门电路构成。

2. 分析方法

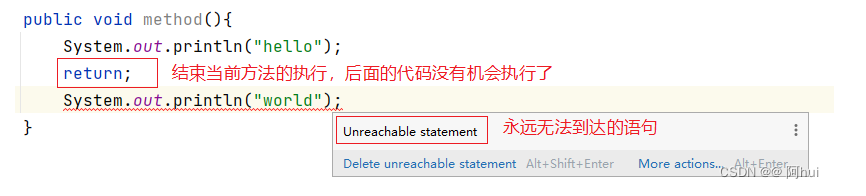

- 根据给定的逻辑电路,写出输出函数的逻辑表达式。

- 进行表达式的变换及化简。直接利用公式或定理对表达式进行变换,也可通过卡诺图的方法进行化简。

- 根据表达式列出真值表。真值表能直接反映出输入变量的取值和输出结果之间的逻辑关系,它直观地描述了电路的逻辑功能。

- 对给定电路的功能进行逻辑描述。根据所得到的表达式和真值表,就可以用文字描述出给定电路的逻辑功能,可以判断出该功能显否满足设计要求。

三、74HC系列门电路

1. 74HC00(与非门)

74HC00芯片有4个与非门,每个与非门有2个输入端。管脚图、逻辑图和功能表见下图。

2. 74HC02(或非门)

3. 74HC04(非门)

4. 74HC08(与门)

5. 74HC32(或门)

5. 74HC86(异或门)

6.编码器

1.编码原理

为了保证编码的位数最短(输出最少),且每一个输入信号对应一个唯一的编码,$n$ 和 $m$ 之间的关系应满足 ${2^{n - 1}} < m < {2^n}$,即输出少于输入。

2.74HC148(8-3优先编码器)

优先编码器(Priority encoder):允许多个信号同时输入,对输入信号无约束,但电路只对优先级别最高的信号进行编码,优先级别低的信号不起作用。

- $\overline {EI} $ 为输入使能端(Enable input),低电平有效。

- 编码器工作时,编码值为输入端口编号所对应二进制值的反码。

- 输出端 $\overline {EO} $ 为使能输出端(Enable output),当编码器工作时,若输入端均无有效输入,则输出低电平,反之输出高电平。

- 输出端 $\overline {GS} $ 用于标识芯片是否产生编码输出。

7.译码器

1.74HC138(3-8译码器)

- ${\overline E _1} = {\overline E _2} = 0$,且${{\rm{E}}_{\rm{3}}} = {\rm{1}}$,译码器工作;否则译码器不工作。

- 译码器工作时,输出信号低电平为有效电平。

2.74HC4511(数码显示译码器)

- $\overline {{\rm{LT}}} $ 全亮测试控制端。

- $\overline {{\rm{BI}}} $ 空白输入控制端。

- $LE$ 输入锁存使能端。

8.数据选择器

${2^n}$ 选 $1$ 数据选择器逻辑函数表达式为 $Y = \sum\limits_{i = 0}^{{2^n} - 1} {{D_i}{m_i}} $

1.74HC153(4选1选择器)

9.数值比较器

1.74HC85(4位比较器)

10.加法器

1.74HC283(4位加法器)

11.触发器

1.74HC74(D触发器)

2.74HC112(JK触发器)

12.寄存器

1.74HC164(8位移位寄存器)

2.74HC194(双向移位寄存器)

13.计数器

1.74HC161(同步加法计数器)