LTC2440 简介

我们使用4-wire SPI接口

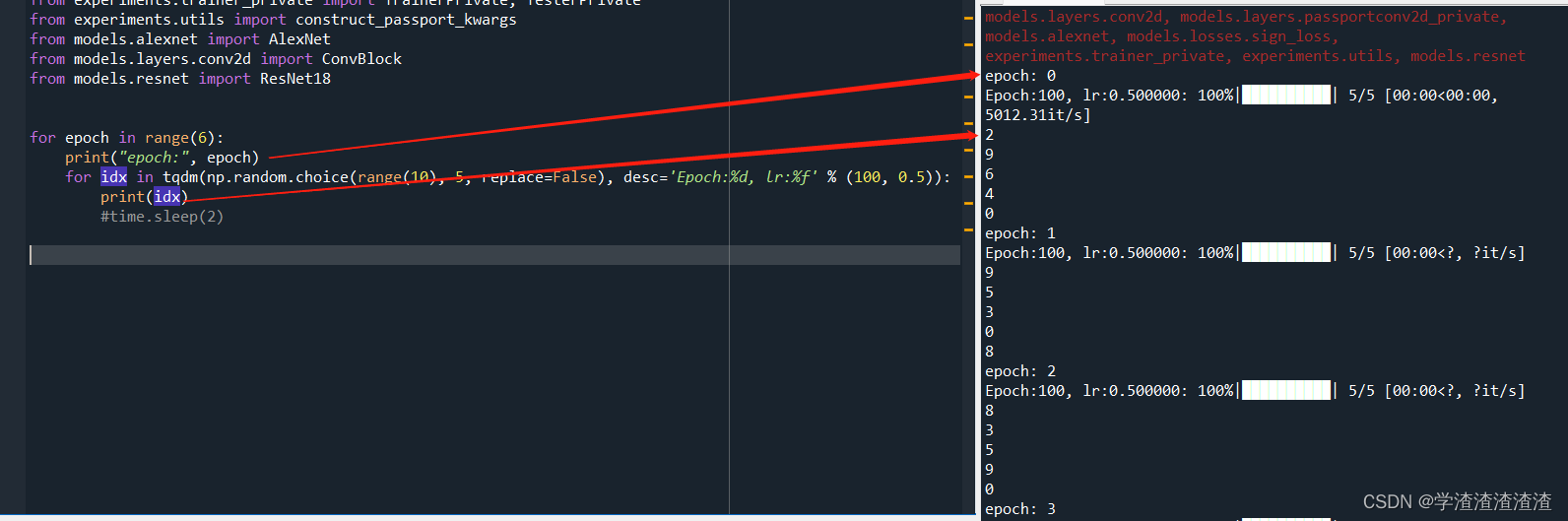

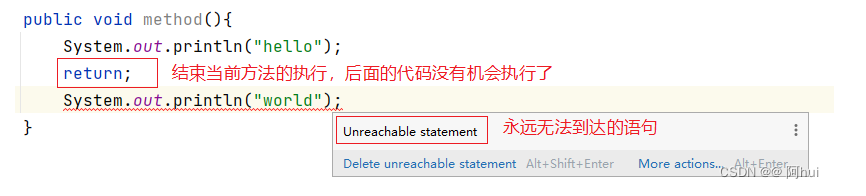

按照时序图上的描述,SDO是在SCLK的下降沿更新数据,那么FPGA接收端就应该在上升沿采集数据。

实际测试发现SDO数据相对于SCLK延迟了60ns,导致采集数据错误

so, what happened? 检查原理图发现,ADC SPI与FPGA之间加入了隔离buffer ,ADC接收到SCLK需要经过buffer,SDO发出到FPGA也需要经过buffer,这会引入一定的延迟

可以看到buffer芯片对应的传输延迟典型就是30ns,这和实际观察的现象是一致的。因此需要在FPGA内部对SDO和SCLK的时序做出调整,简单的,在SCLK的下降沿采集SDO即可。