项目芯片介绍

在项目中负责什么?有什么难点?如何实现?

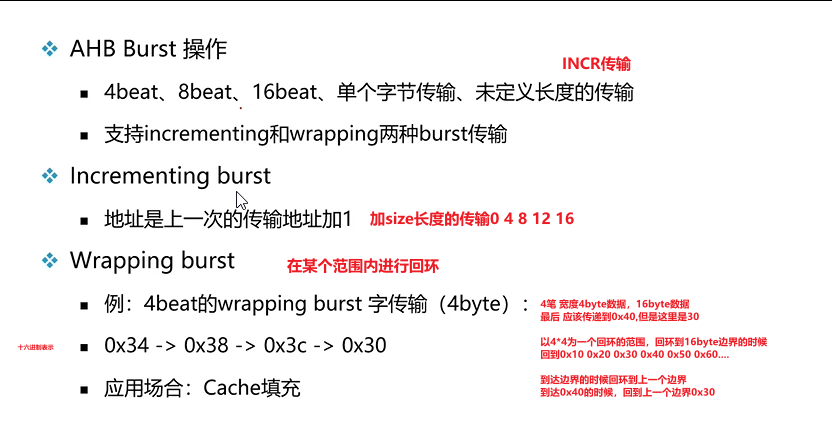

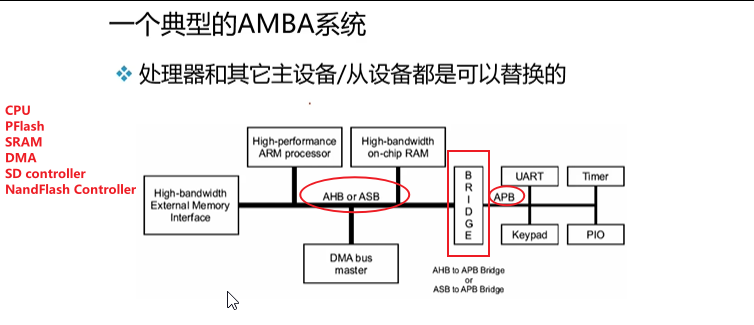

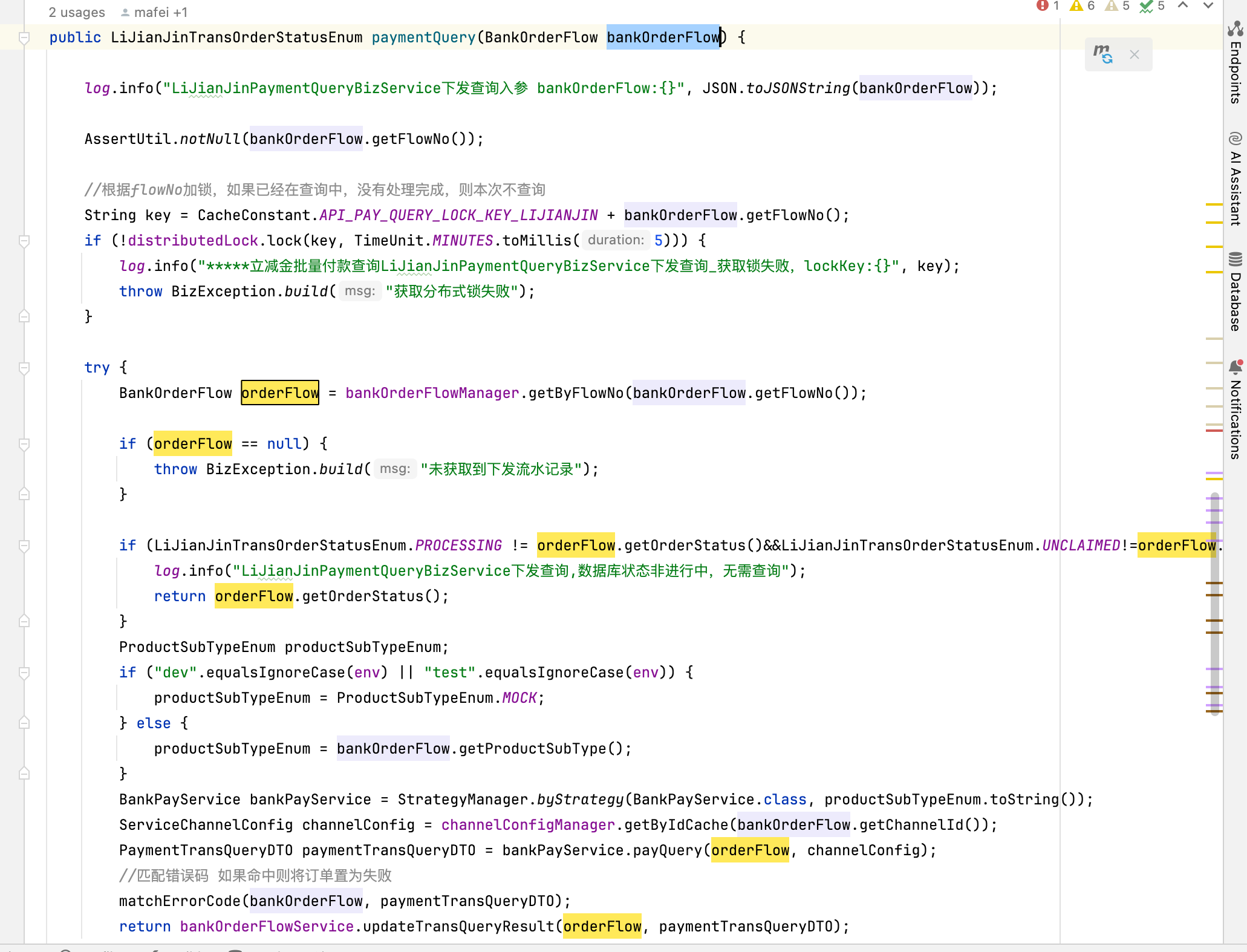

- 总线原理-AMBA总线(AHB,APB总线)

简介

需求

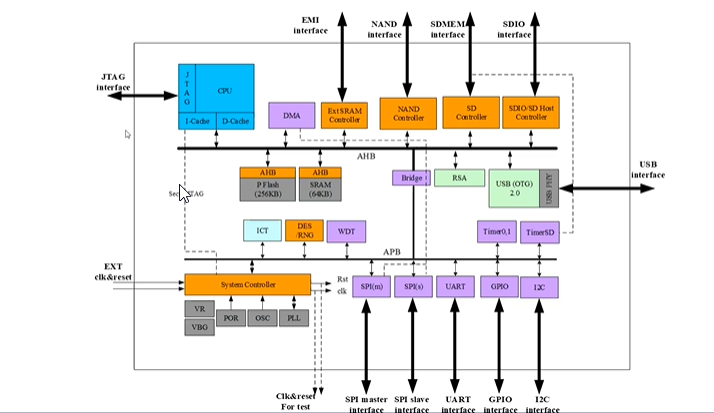

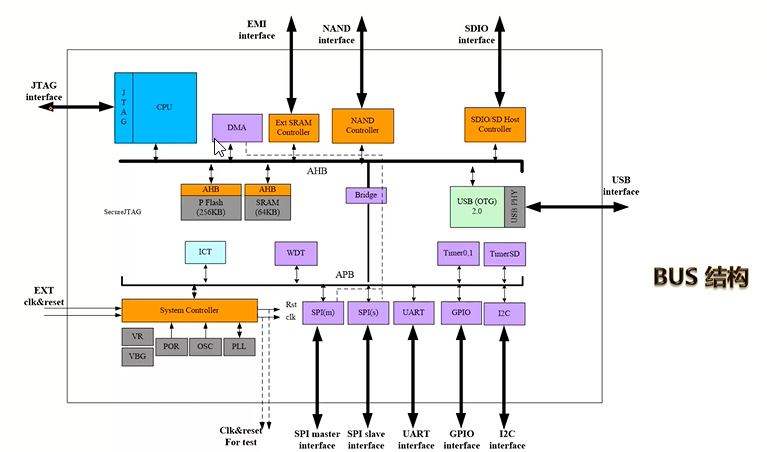

需要了解需求(芯片需要哪些模块,与哪些接口通信),这个项目是一个MCU的芯片,MCU中集成了一个轻量级的CPU,CPU以当前ARM的芯片为例(A系列芯片,M系列芯片)。

- 芯片需要与外界进行通信,SD接口,USB接口。

- 芯片具有计算功能,CPU和加速器进行一些计算,处理的数据需要存储,就需要存储器。NandFlash存储需要芯片内部有NandFlash控制器。

- 芯片需要有高速总线和低速总线。

- 项目芯片集成了32位CPU,包含SD,USB,NandFlash,SPI等高速通许接口以及GPIO,URAT,I2C等通用芯片。

参数

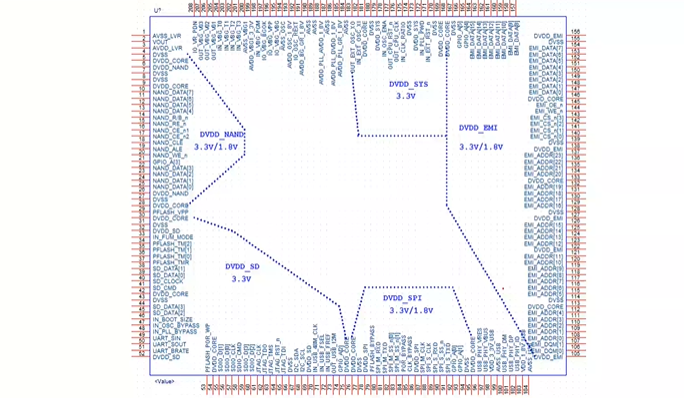

芯片内核电压:1.8V(电压越大,性能越高,功耗越高)

芯片IO电压:3.3V/1.8V(在IO中国有level shifter,可以升压或者降压,IO入口一端是高压,内核处是低电压)

芯片工艺:TSMC 018 Flash process(工艺决定了PPA,工艺越高,流片成本越高;Flash工艺,可以进行一个片上Flash集成)

芯片IP:DW IP;Analog IP;Soft IP

- 软核(Soft IP Core)

供应商提供的VHDL的方式提供的IP,自己团队或者是外包进行DC和后端设计。可以给后端实现提供较大的空间。 - 固核(Firm IP Core)

提供的是一个网表,将RTL进行了综合。 - 硬核(Hard IP Core)

具体形状已经确定了,在SoC中要预留硬核IP的位置空间。硬核IP的定制化程度比较低。

模块

- CPU - M系列轻量级处理器(32位)

之前很多芯片都是使用的ARM的架构,成本较高;但是现在很多低端的芯片使用的是risk-V架构芯片(开源架构)

RISC-V(发音为“risk-five”)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA) - 片上存储器

需要data存储器和instruction存储器,需要在片上规划存储器,提升CPU的访问存储执行效率,使用片外的存储器效率低。

256k 程序Flash,其中8k/16k用于boot,其余用于UserCode

64k SRAM,支持单周期读写 - DMA控制器

因为芯片中有很多存储器,所以需要实现存储器之间的信息通讯和传输,就需要DMA控制器。

这个芯片提供三个独立的DMA通道,分别用于momery-momery,momery-spi(慢速通道),spi-momery的传输,三个通道可以同时使能

DMA是挂载在总线上的使用的AHB总线,主要参数Burst Size,transfer size等可以配置 - 中断控制器

提供32个中断源;中断优先级可以配置

在计算机中,中断控制器是一种集成电路,可帮助微处理器或CPU处理来自多个不同源(如外部I / O设备)的中断请求(Interrupt Request,以下简称IRQ),这些中断请求可能同时发生。中断控制器有助于确定 IRQ 的优先级,以便CPU在得到 IRQ 的相对优先级评估结果后,切换到最合适的中断处理程序 (Interrupt Service Routine,以下简称ISR)。

中断器原理简介

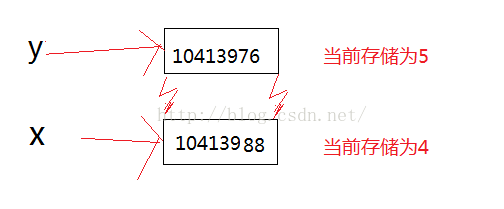

首先引出中断产生的原因,对于CPU而言,假如没有中断的概念,CPU会根据指令在内存中的存放顺序,依次取指,解码,执行通常情况下PC的值一般指向下一条需要处理的指令地址。

当程序顺序执行时,PC每次根据指令字节数增加相应的值。以32位指令解码为例,每执行一条非跳转指令的情况下一般是增加4字节。执行过程中,若遇到跳转/返回指令,则跳转/返回到对应的PC地址执行。

中断工作原理:计算技术里中断过程,就是主芯片的外部信号或内部信号,中断了该芯片正在执行的程序,主芯片转而处理由该信号引发的其他程序,结束后再回到中断的“断点”,继续执行原有程序。 - Timer/Watchdog

提供3个独立的Timer,提供32bit的Watchdog

watchdog简介

看门狗,又叫watchdog timer,是一个定时器电路,一般有一个输入,叫喂狗(kicking the dog/service the dog),一个输出到MCU的RST端,MCU正常工作的时候,每隔一段时间输出一个信号到喂狗端,给 WDT清零,如果超过规定的时间不喂狗(一般在程序跑飞时),WDT定时超过,就会给出一个复位信号到MCU,使MCU复位。防止MCU死机. 看门狗的作用就是防止程序发生死循环,或者说程序跑飞。

外部接口

- SD Host接口

SD Host兼容SDmem1.01和2.0协议 - 外部存储器接口

支持对片外SRAM,PSRAM,norflash的访问(16bit)

提供四个片选,每个片选32M空间 - NandFlash接口

支持8bit SLC/MLC NandFlash

支持2k,4k,8k page size

支持硬件ECC纠错,ECC纠错能力(16b/24b/30b)/kb

兼容onfi2.0规范(注意协议的版本) - SPI master/slave接口

支持4-16bit传输

提供RX,TXfifo

支持DMA - UART 接口

波特率可配置

支持8、9bit等数据格式

支持硬件奇偶校验 - GPIO接口

提供20个GPIO,其中6个独立,14个复用

提供5个用中断功能的GPIO,中断触发模式可配置 - JTAG调试接口

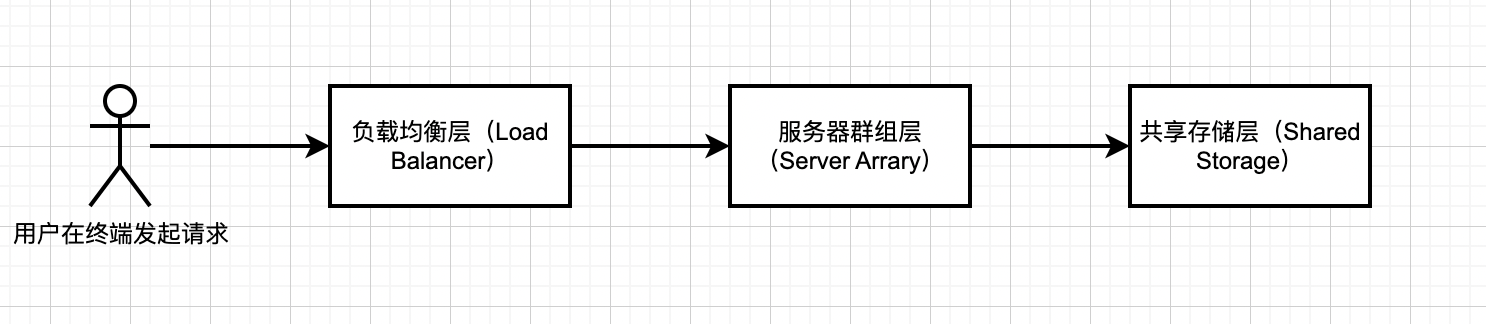

架构

- AHB和APB总线通过Bridge进行连接,AHB作为主访问,APB作为从访问。只存在AHB到APB的访问,不存在APB到AHB的访问。

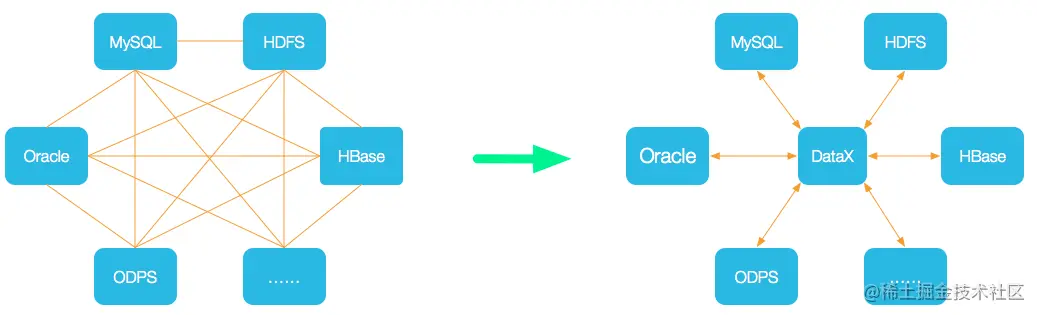

几种IP互联接口标准

- IBM-CoreConnect(PLB/OPB/MCR)

- ARM-AMBA

- Silicore-Wishbone(OpenCore)

- OCP

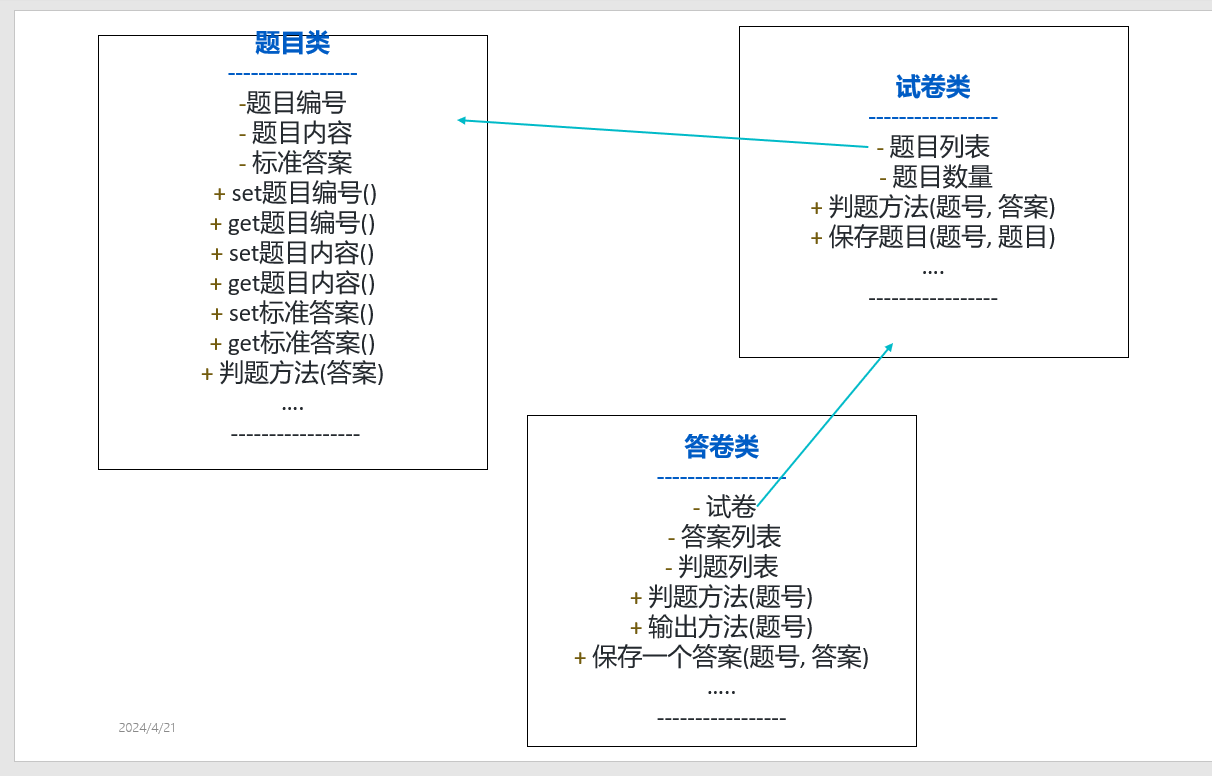

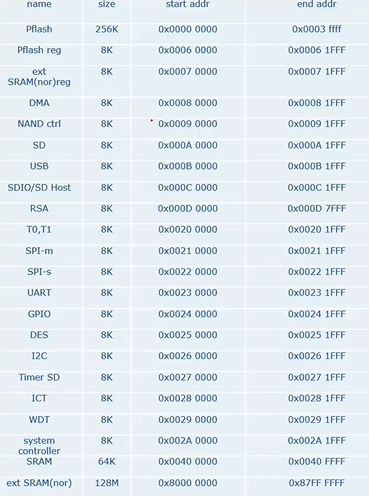

IP地址

- 选择AMBA总线作为互联协议之后,如何区分总线上的不同的模块?通过不同地址空间的划分进行区分,给每个IP划分一个地址段;CPU访问一个模块的时候会去查找memory map表,查到相关的地址段之后,就会访问该地址段的模块。

- AHB总线上最下的地址空间是1k

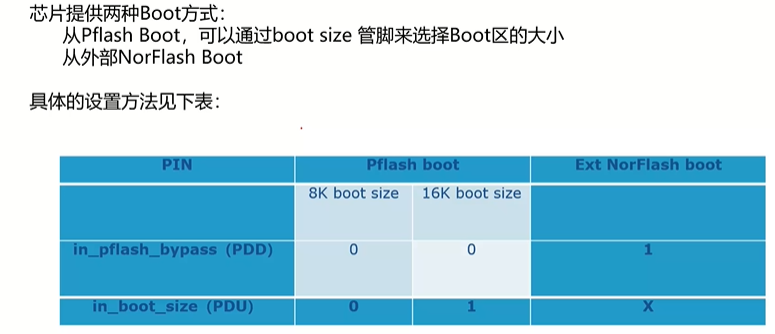

boot(初始化)方式

boot就是芯片上电之后对于不同的模块进行初始化的过程,初始化之后Soc才能正常进行运转。

芯片提供两种Boot方式

- PFlash boot(Int)

- Ext NorFlash boot

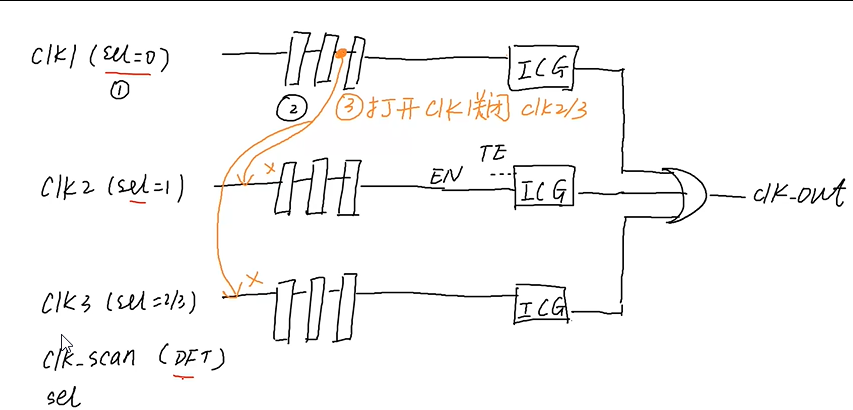

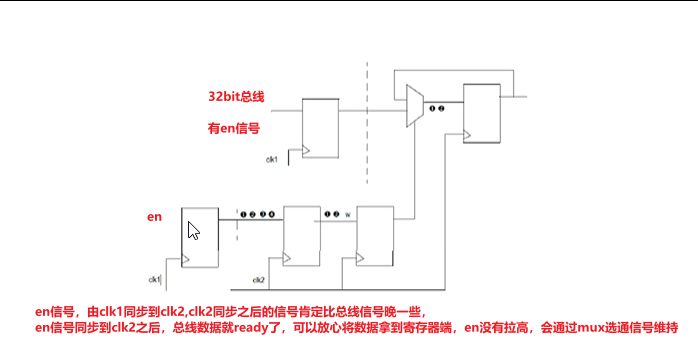

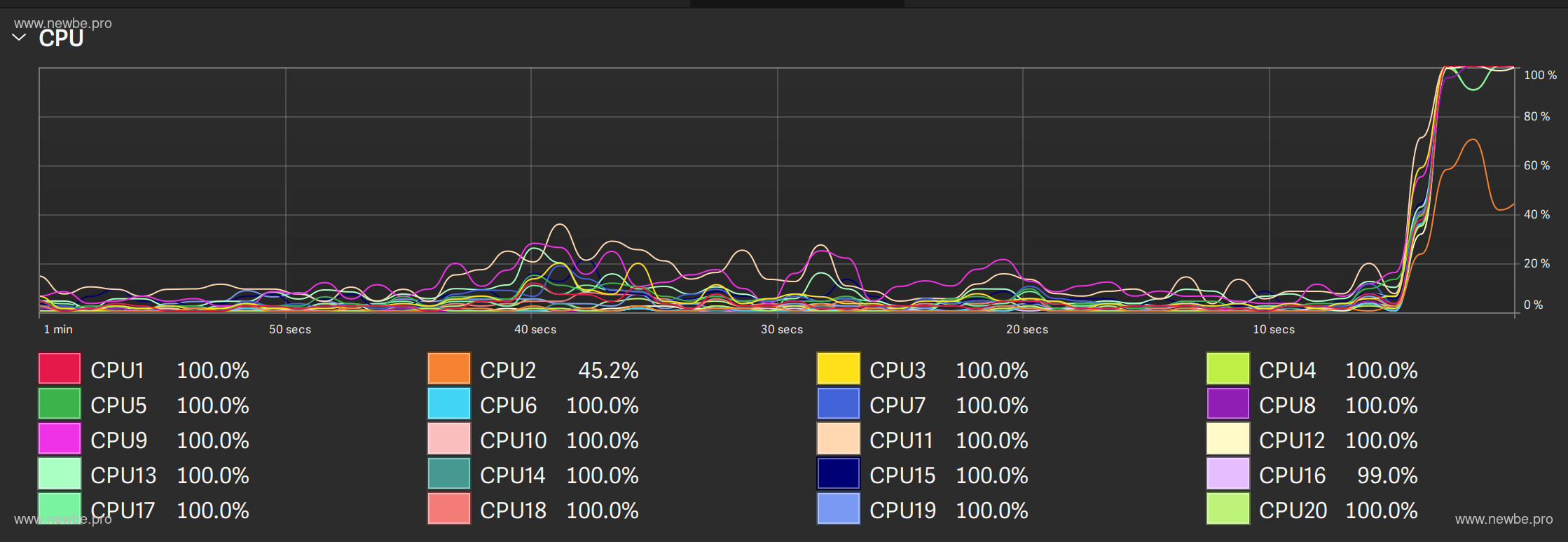

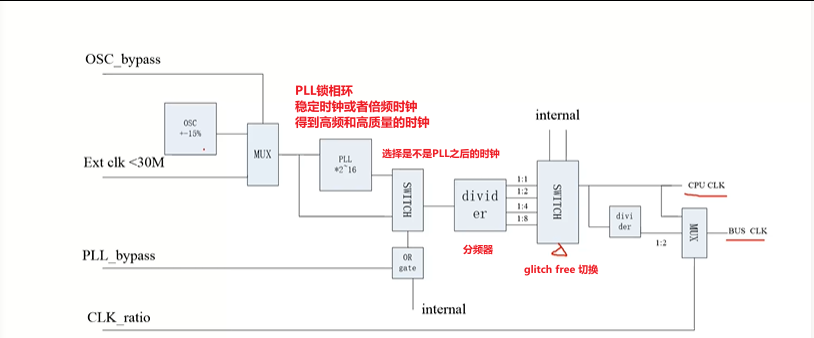

时钟架构

芯片架构除了功能模块划分,还需要进行时钟划分,所有的模块都需要时钟进行驱动。如果在SoC运作过程中时钟出现问题,整个SoC的功能都会出现问题。

- 输出有CPU时钟和BUS时钟

- 数据量传输大,就选择没有分频的时钟;数据量比较小,可以使用二分频的时钟,通过选择时钟进行降低功耗。

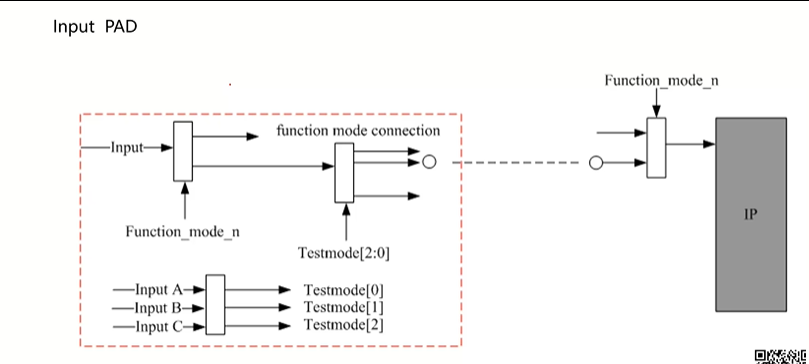

功能模式

- Function Mode

芯片进行处理的时候的模式 - DFT Mode

DFT,对于组合逻辑或者寄存器形成扫描链(scan_chain),通过scan_chain判断是不是功能正常。

Logic_scan_mode

CPU_test(CPU scan)

Analog_test

USB_phy_test

Pflash_test

通过PinMux模块(IO),进行pad复用 - 正常在芯片内部形成scan_chain之后,用于测试的激励信号会来自与外部的基台,但是SRAM是不同的。

- SRAM通常使用MBIST进行测试,SRAM一起集成的bist会自己产生激励,SRAM会读取bist的输出传递给bist,bist会有比较逻辑进行判断SRAM是不是完好--自建内测试。

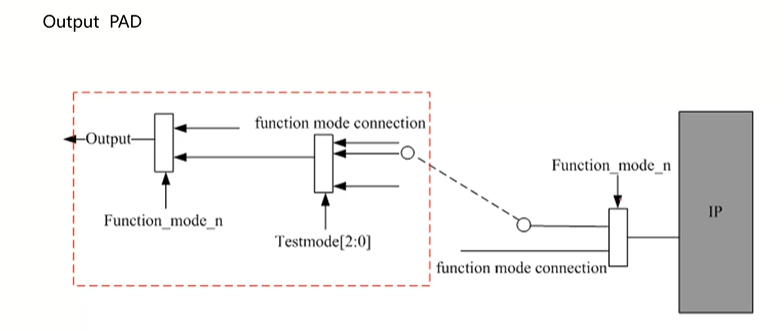

Pinmux

芯片的引脚是有限的,但是很多模块都需要IO,如果给每一个IP都分配IO引脚就会造成引脚数量过多,为了解决这个问题,需要进行引脚的复用。

通过mux进行选择,

- 输入信号,进行多选1

- 输出信号,可以进行汇总输出

芯片的集成层次

- core

主要包括AHB,APB总线以及总线上的各个模块 - Top

主要包括core,cpu,clk_rst产生模块,Macro Wrapper,pinmux模块 - Top_pad

主要包括芯片的所有PAD,VR以及输出buffer

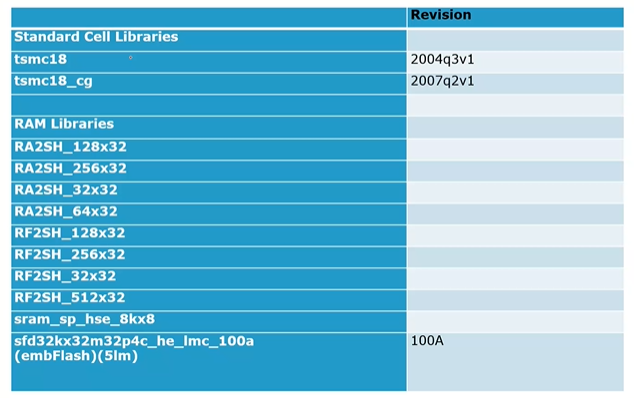

Libraries

- 选择好工艺之后,会有工艺库,其中包含standcell,SRAM...

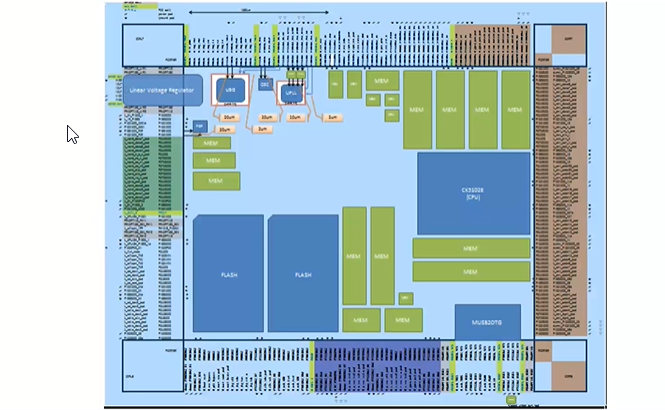

物理设计

FloorPlan

- FloorPlan的输入是整个芯片的数据流

电源分布

封装形式