CDC设计实例

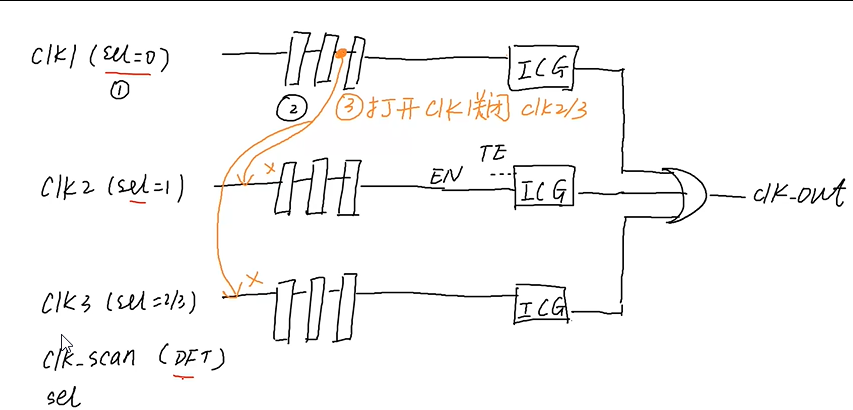

Clock Gating Cell & Glitch Free Clock Switch(门控单元和动态切换时钟)

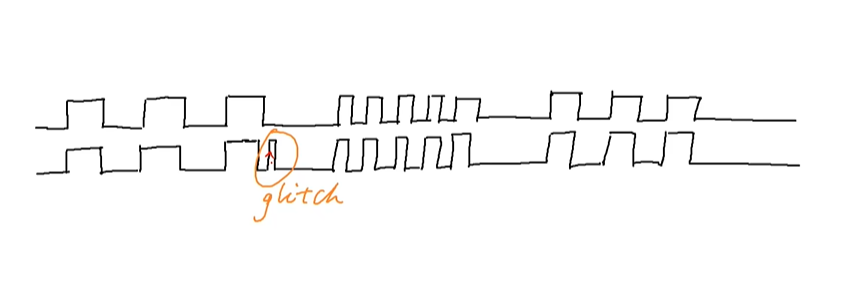

一个电路有多个时钟输入进来,希望在工作当中能够动态切换时钟;比如CPU根据工作负载(AI或视频处理),工作负载大,时钟频率快,功耗高,工作负载低(浏览图片或者待机),时钟频率低,功耗低,切换时钟频率,希望能够动态切换时钟;通过动态切换时钟,以减少功耗;Glitch(差错),在时钟切换过程中不能出现毛刺

普通组合逻辑信号送到寄存器D端,在时钟的有效沿进行采样,只要组合逻辑信号能够满足建立时间和保留时间,即使信号经过组合逻辑出现一些毛刺也没有关系,因为这些毛刺只是在稳定信号之前和采样之前出现的,经过一段时间能够稳定就可以了

如果时钟产生无效的毛刺,时钟直接进入寄存器,会产生一些无效毛刺,首先会导致采样一些错误的值,另外产生的毛刺可能不是时钟周期预期的值,可能会产生亚稳态

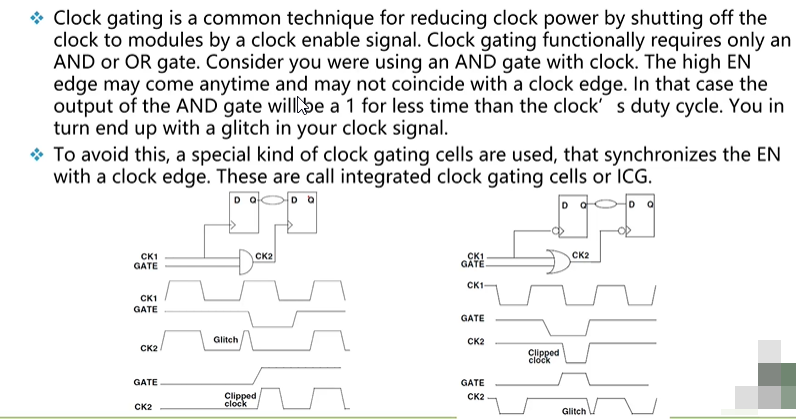

Clock Gating 和 Clock Switch模块在工作中会有现成的模块,会有Fab提供

- mux sync

- 门控单元:clock gating(Fab或者是standcell会提供ICG门控单元)

- 动态时钟切换:glitch free clock switch

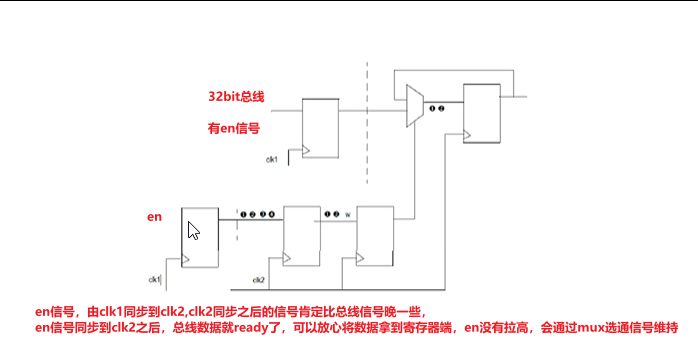

mux sync

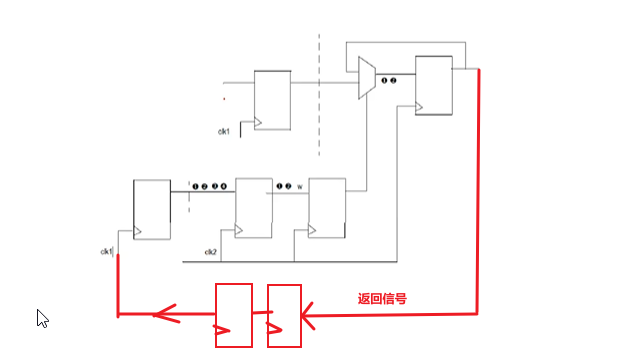

上述信号在进行传输的时候,寄存器端拿到数据之后需要进行返回信号,告诉输入端进行下一笔数据的传输

- mux sync通常被做成公共模块,这种模块需要知道在哪里进行调用,自己写的模块需要上报路径和使用的位置

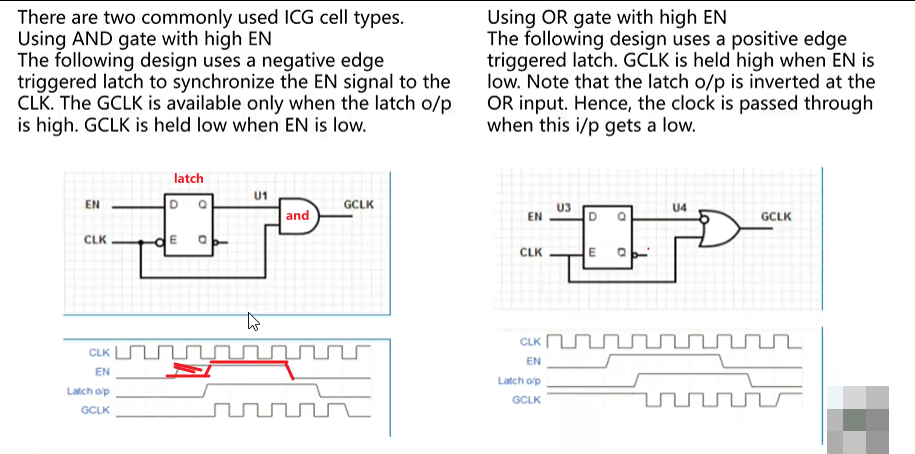

ICG(Integrated Clock Gating)

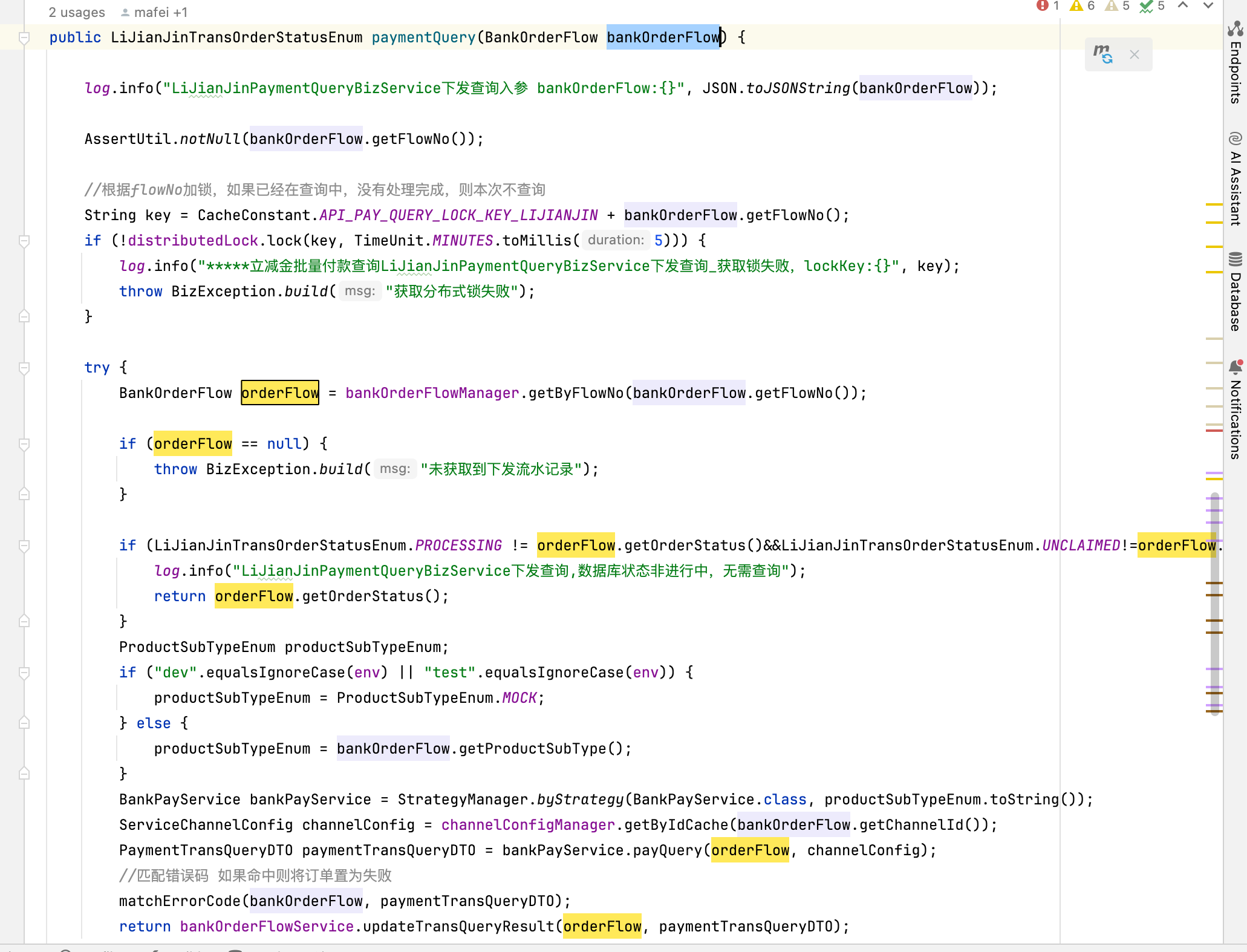

ICG代码(behavior model)

module cell_clock_gating(TE,E,CP,Q)

input TE; // test enable which is used for test mode in DFT

input E ; // enable

input CP; // clock

output Q; // output signal

reg E_lat; internal signal

assign E_or = E | TE; //

always @(CP or E_or) // this is a latch,不是时钟上升沿和下降沿有效的,是latch

begin

if(!CP) begin

E_lat <= E_or;

end

end

assign Q = E_lat & CP;

endmodule

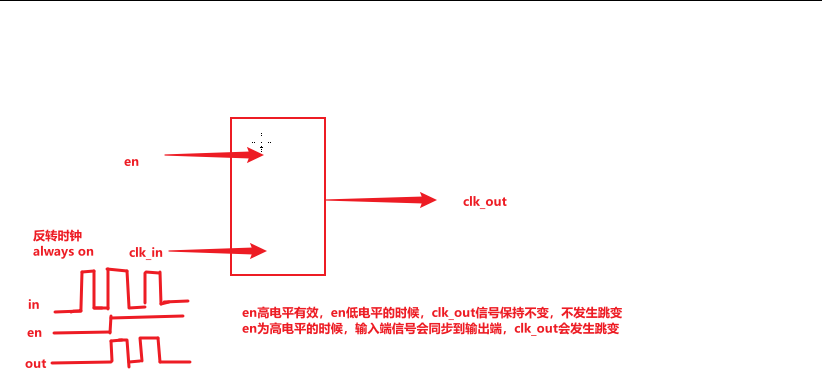

- latch是有效的电平期间,进行采样,在无效的电平期间进行保持

- CP是时钟输入,在enable为高的作用下,原始输入同步到Q端,如果enable为低的情况下,不让Q端进行反转,固定Q端的时钟信号

- Q = E_lat & CP - 为了消除毛刺,latch在低电平的时候发生变化,在CP为低的时候,latch会产生变化,有可能产生毛刺,但是此时通过与门,Q端一定为低信号(不管E_latch是什么值,有没有毛刺)

- 这个代码只是一个功能模型,给仿真使用,不能用于综合

- en信号为低的时候,输出时钟是不反转的,时钟不反转,动态功耗就会很低。

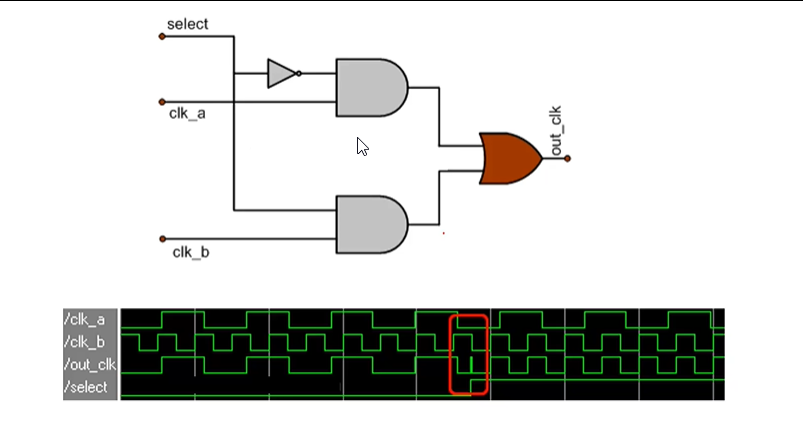

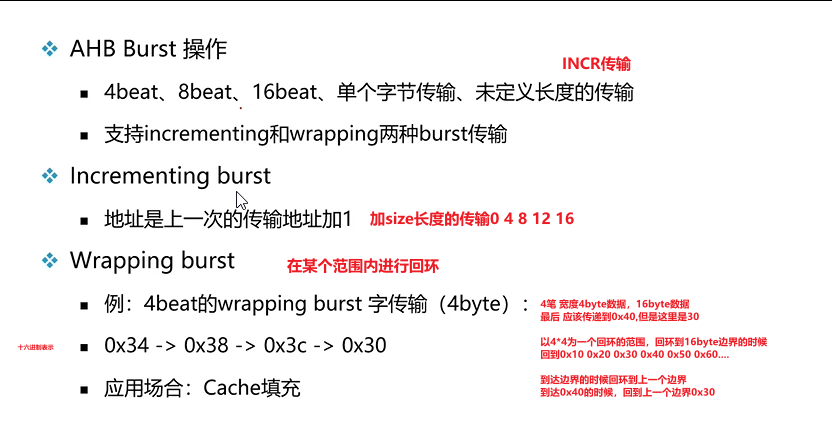

Clock Switch:Glitch due to simple mux

假设有两个时钟,clk_a频率高,clk_b频率低,如下图所示,select信号为低的时候选择的是clk_a,select为高的时候选择的是clk_b,当select信号从低到高进行跳变和clk_b信号从高到低进行跳变的时候,会出现毛刺,这中毛刺作为时钟信号的时候出现需要进行规避

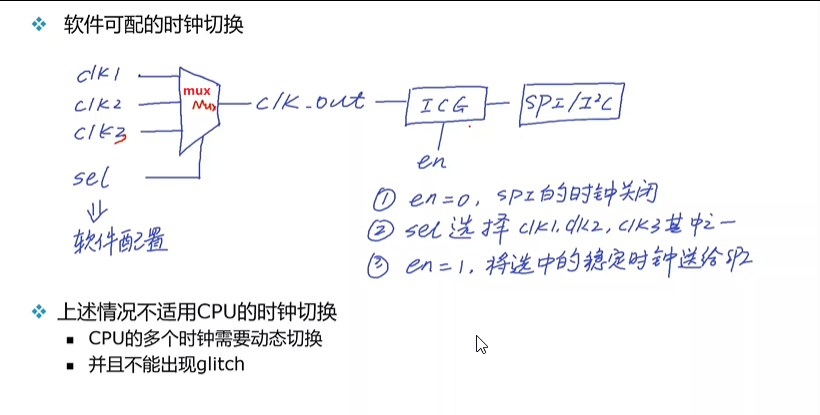

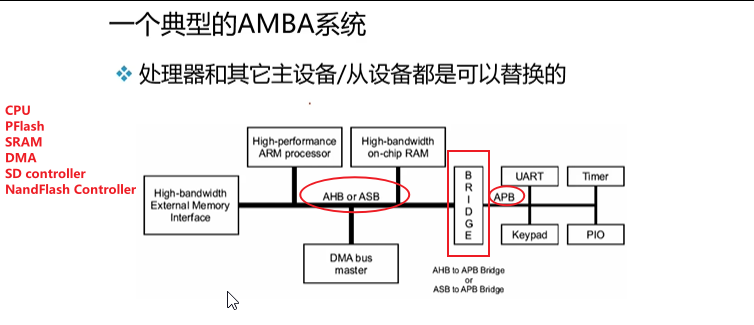

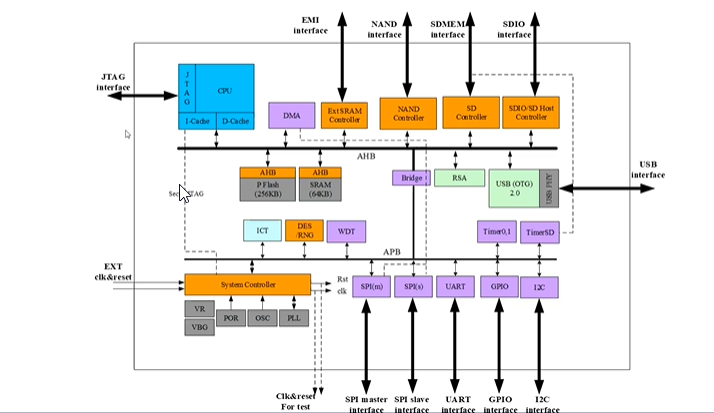

SoC系统中时钟切换应用场景

- 进行时钟切换的时候先将ICG的enable=0,不管前面clk输入如何,ICG输出为0,可以滤掉毛刺;在enable=0得时候更改sel选择clk,有可能会产生毛刺,即使有毛刺输出也一直为0;选择完成之后将enable拉高,得到最终呢选择的时钟信号

- 驱动的是SPI,I2C模块,信号传输速率比较慢,使用软件配置的方式也比较慢,这种模块可以使用这种方法;如果设计高性能模块(比如CPU),要求速率很快,这种方法不适用

- CPU是整个SoC的核心,CPU通过分发指令和任务可以调用DMA、NAND Controller等模块,CPU是SoC的大脑;使用软件配置的方法切换时钟,速度慢,会拖缓整个SoC效率

- CPU在动态切换的时候是不能出现毛刺的,如果出现毛刺,会导致CPU取址错误,从而导致功能错误

![[数据结构] 栈 (C语言)](https://img2023.cnblogs.com/blog/3039354/202301/3039354-20230119211454737-2099370575.jpg)