Verilog Simulation Event Queue

主要了解VCS是如何处理交给它的代码的

Verilog的仿真事件队列,介绍VCS如何处理交给它的代码。VCS是Synopsys公司的,支持多种语言。

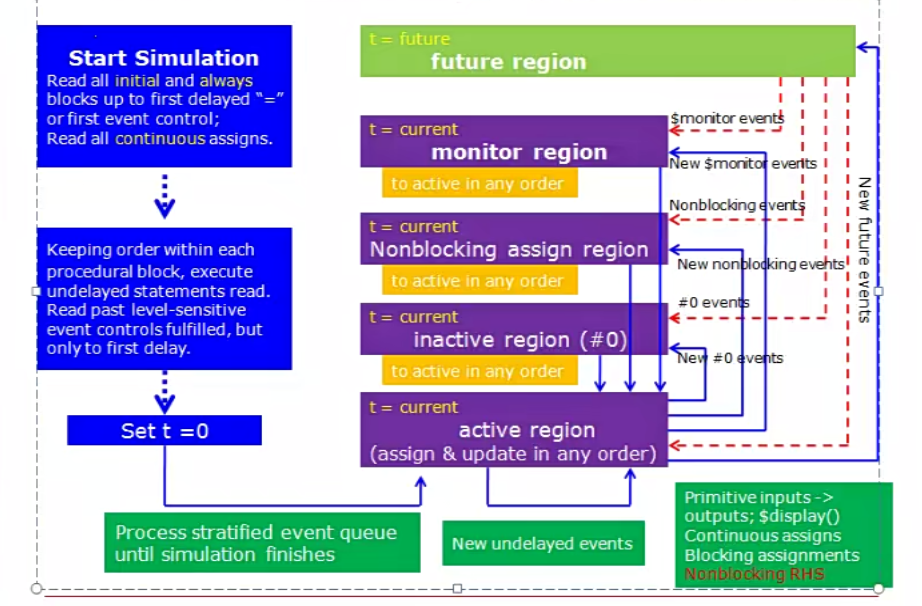

1.Verilog 仿真事件队列

Verilog内建仿真规范

- IEEE1364,Verilog语言的仿真基于分层的事件队列

- 执行事件的队列

- 仿真时间的计算

- Verilog仿真器先从没有延迟的事件开始,执行他们,然后把时间设为0,然后按照时间顺序依次执行各个事件。

- Verilog语言规范没有规定当多个事件被安排在同一时刻来调度时,因该执行哪个。

- 只要在同一层次的事件,什么执行顺序都是可以的

- 在CPU的环境下,或者是说在软件的环境下,指令的执行是串行的。单核CPU是串行的,多核CPU是并行的。硬件电路与软件的区别就是并发的执行性。如何通过软件模拟硬件的并发性非常重要,仿真器仿真的时候,相同的代码交给不同厂商生产的厂商出品的仿真器,结果可能不同。

- 仿真器设计出来有一定的算法,首先按照一定的标准去做,有自己的内建实现标准。

- 设计师必须理解Verilog的分层仿真事件队列

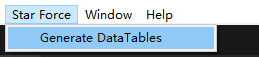

2.VCS处理代码的流程

VCS如何处理交给它的代码

- VCS会将模块代码读入,将代码中的always和assign读入,按照顺序放到一个队列中。

- 先执行一些没有延时的语句,比如初始化的语句(变量的初始化,initial)。执行了没有延时的语句之后,设置当前时间为0,current_time=0。

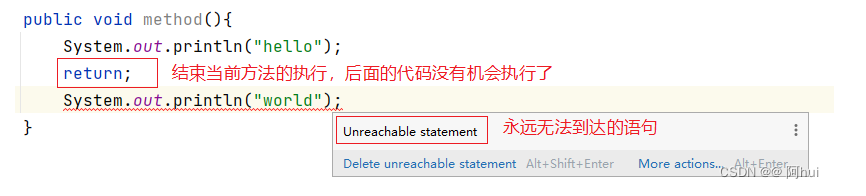

- 进入active region

- Verilog首先会执行一些源与,在Verilog中有简单的与门、或门、非门、PMOS、COMS,执行是没有时间的

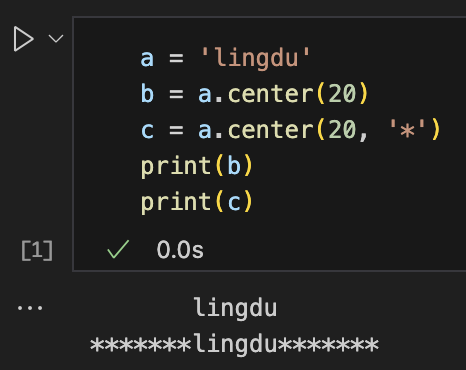

- $display()--是没有任何延迟的

- assign--没有延迟的assign语句

- Blocking assign--阻塞赋值,=,首先将右边的表达式计算出来,同时赋值给左边的部分。阻塞赋值在active区的两步全部完成

- Nonblocking RHS--非阻塞赋值(<=),只计算出(<=)右侧表达式的结果,并不进行完成赋值。非阻塞赋值在inactive区只完成一部分

- 进入inactive region,在RTL代码中使用#0,虽然表示没有延迟,但是实际执行的时候是在inactive区(#0)--首先执行active区,inactive区执行#0延时的,虽然#0表示延迟为0,但是执行的区域是不同的。

- 进入Nonblocking assgin region--完成非阻塞赋值的赋值操作

- 进入monitor region--$monitor events系统函数与display相似,但是不同。

- $monitor系统函数在monitor region执行;display在active region

- $monitor后面跟几个变量,比如a,b,c,只有在变量发生变化的时候,monitor才会执行。也就是说,如果用monitor监测一个非阻塞赋值变量得到的是赋值之后的新值;用display监测非阻塞赋值变量,得到的是没有赋值之前的旧值。

- 进入future region处理其他的语句。

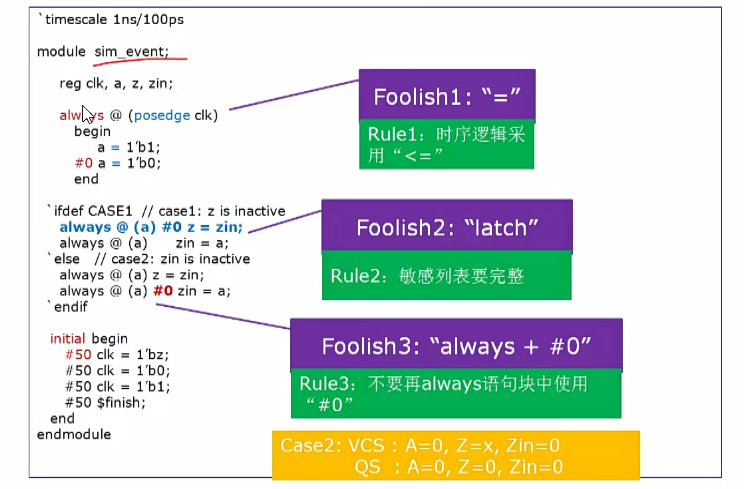

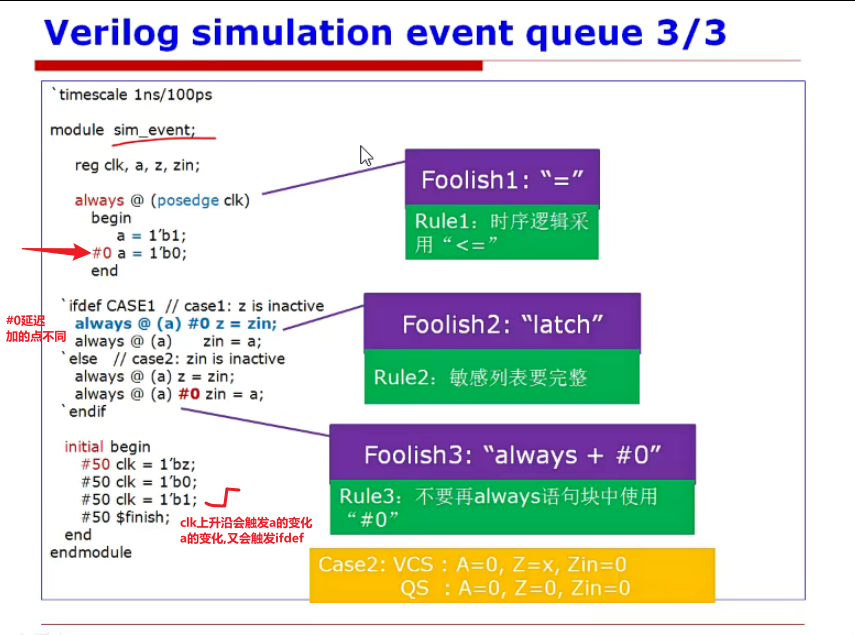

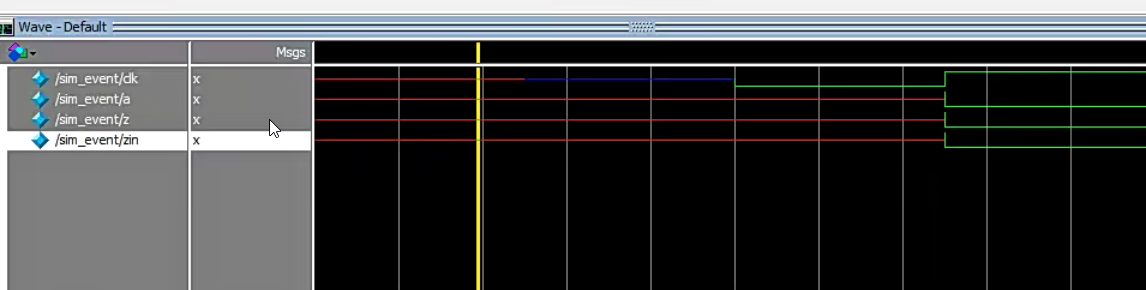

3.VCS事件队列例子

- 上升沿来的时候,#0延迟是执行在inactive区的。

- ifdef-条件编译,就是告诉编译器,如果CASE1宏定义了的话,执行下面的语句,没有定义执行else语句;

`timescale 1ns/1ns

`define CASE1

module sim_event;

reg clk,a,z,zin;

always @ (posedge clk) begin

a = 1'b1;

#0;

a = 1'b0;

end

`ifdef CASE1 // case1: z is inactive

always @ (a) #0 z = zin;

always @ (a) zin = a;

`else

always @ (a) z = zin;

always @ (a) #0 zin = a;

`endif

//generate clk

initial begin

#50 clk = 1'bz;

#50 clk = 1'b0;

#50 clk = 1'b1;

#50 $finish;

end

endmodule

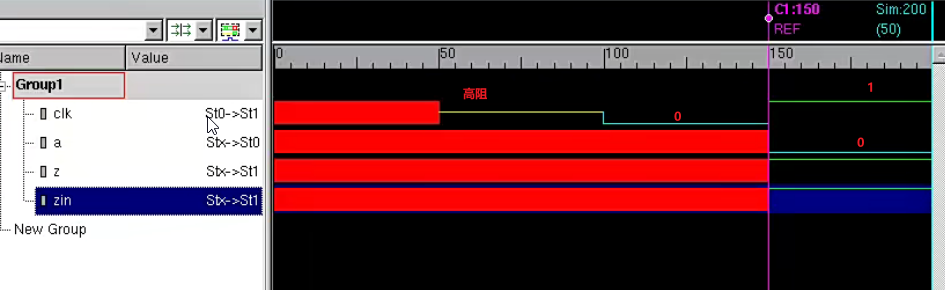

3.1 不同仿真器的仿真结果

VSC仿真

- a z zin - 0 1 1

modelsim仿真

- a z zin - 0 0 0

相同的代码,在不同的仿真器,结果不同,严格来说是没有对错之分的,首先符合语法规范

3.2 问题

- 时序逻辑-always中是不建议使用阻塞赋值,要使用非阻塞赋值

- always中不允许使用#0

- 缺失reset复位信号

- 对于使用always语句生成组合逻辑,一般使用always(*)用于产生组合逻辑电路

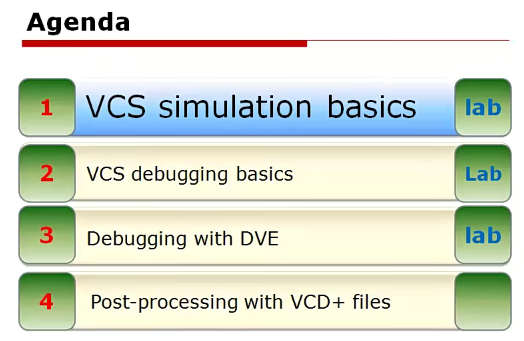

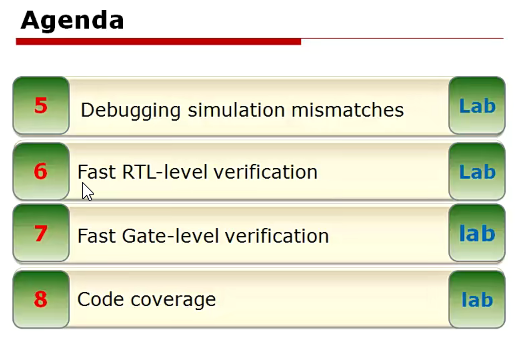

4.数字逻辑仿真工具VCS

VCS支持数字逻辑仿真工具,不适用于逻辑

- 数字电路和verilog

- linux操作系统及GVIM(VI)文本编辑器

- Gate-Level regression -- 后仿

- coverage(覆盖率)--代码覆盖率和功能覆盖率

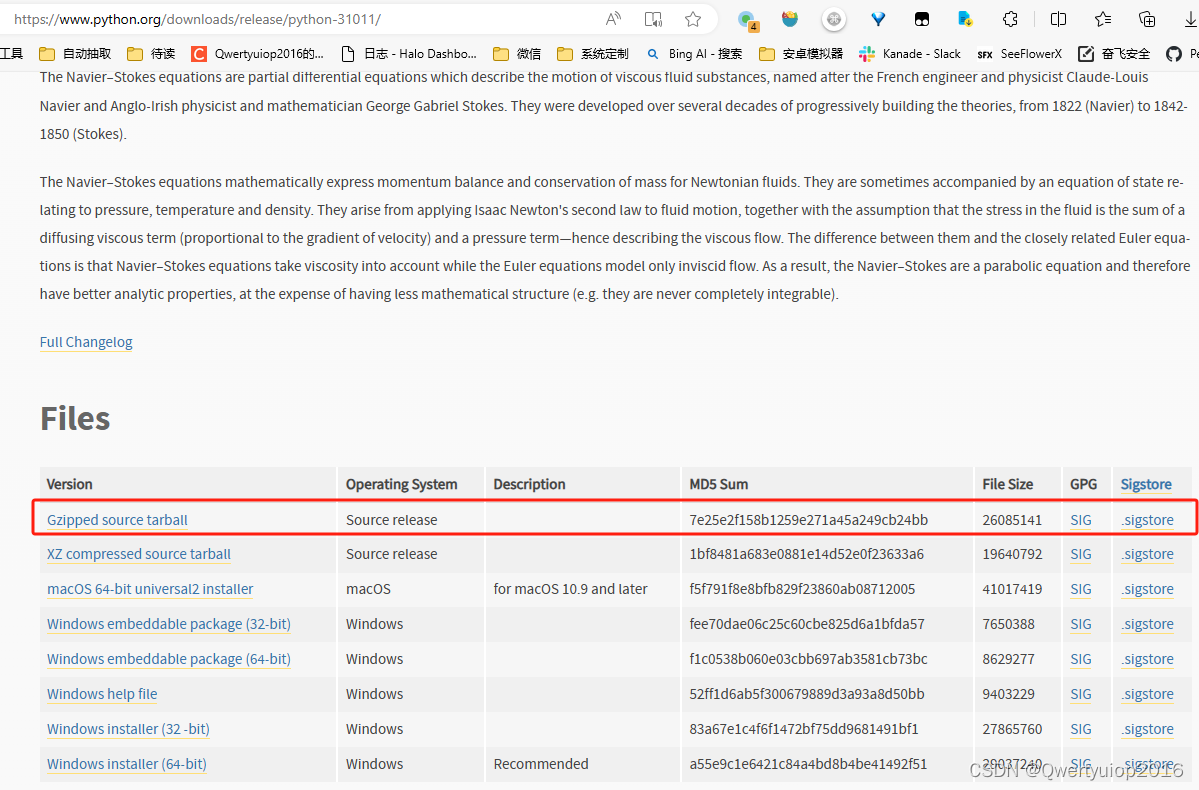

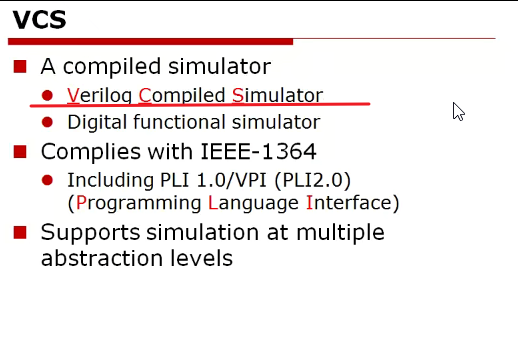

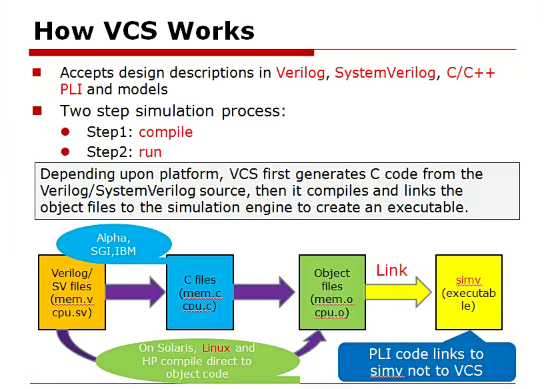

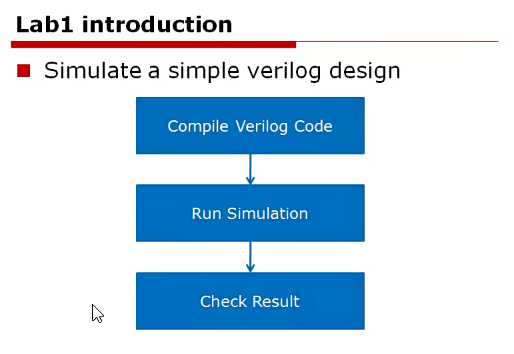

5.VCS仿真过程

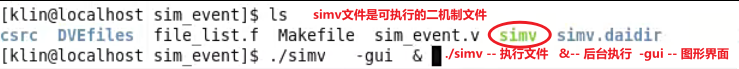

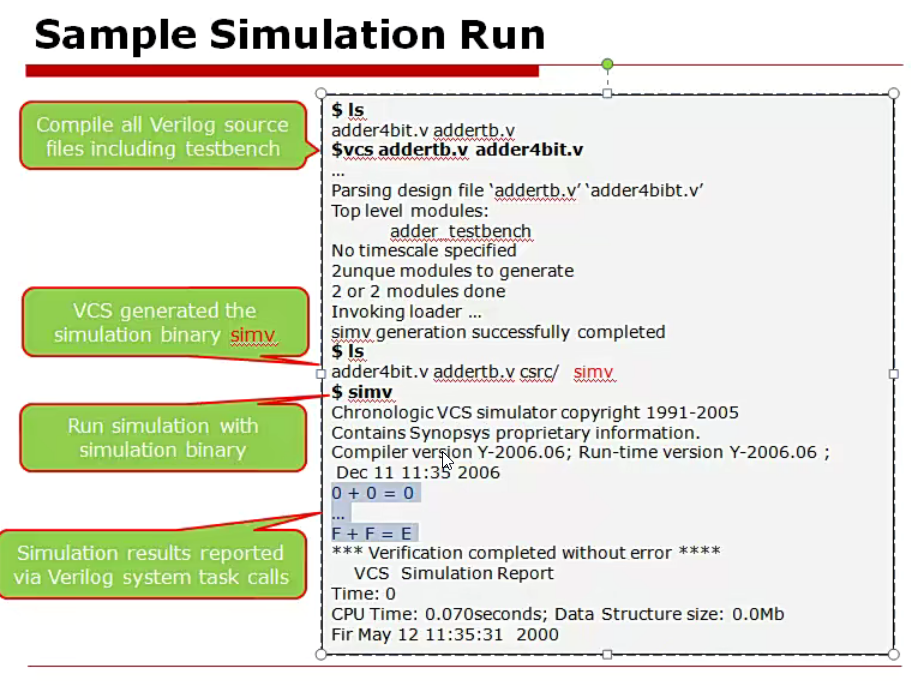

VCS是编译型逻辑仿真工具

- 首先将RTL编译成二进制可执行文件

- 执行仿真

- 符合IEEE-1364标准

- 通过PLI接口调用C语言或者是C++写的程序

- 支持多个抽象级别的仿真(行为级描述(验证用的多),RTL级(设计用的多),门级(RTL级经过综合之后得到的,与具体的工艺库相关tsmc,smic,csmc))

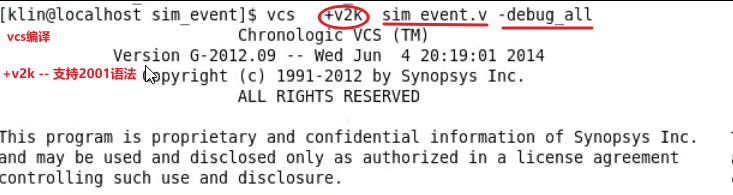

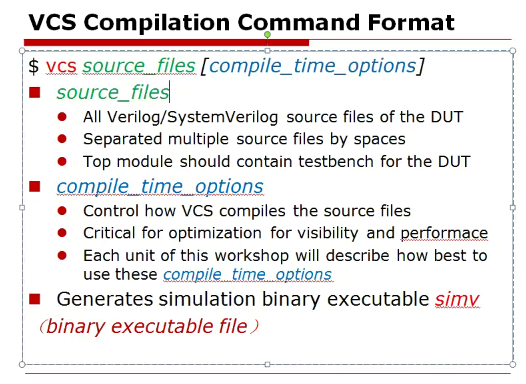

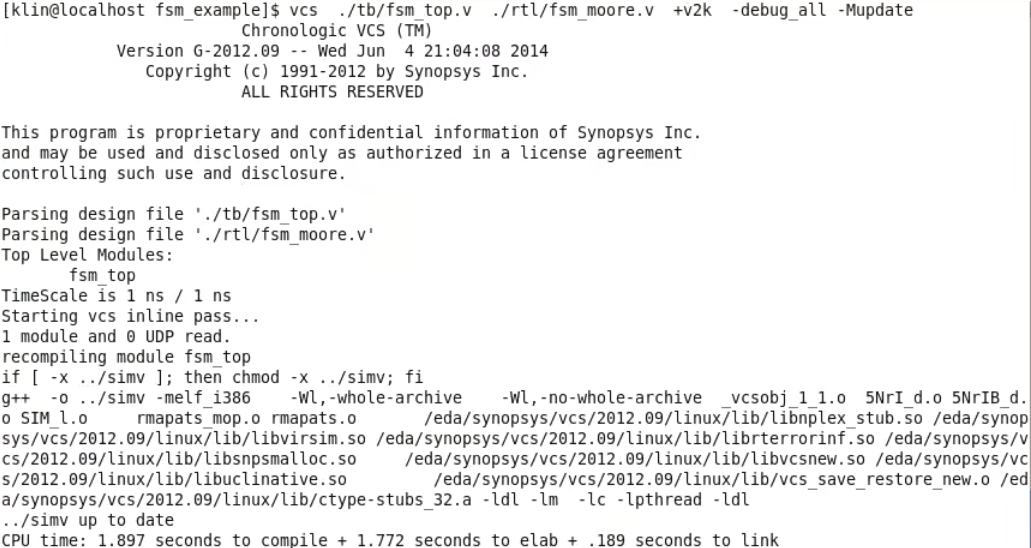

6.VCS编译命令及选项

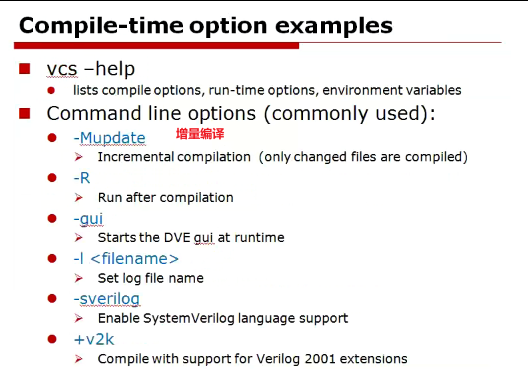

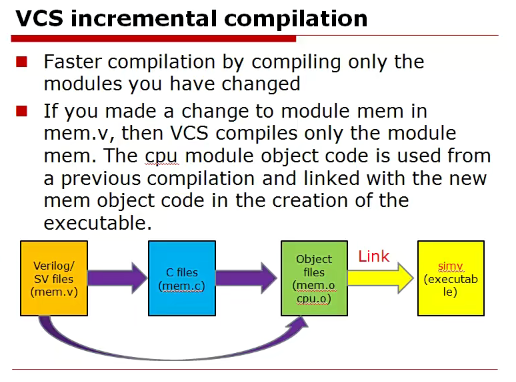

- 增量编译,如果现在设计有100个RTL.v文件,验证文件有1000个文件,如果要修改其中的一个文件,如果重新编译会花费很长的时间,使用增量编译,将修改的一个文件进行编译,和其他文件的.o文件做链接生成二进制执行文件

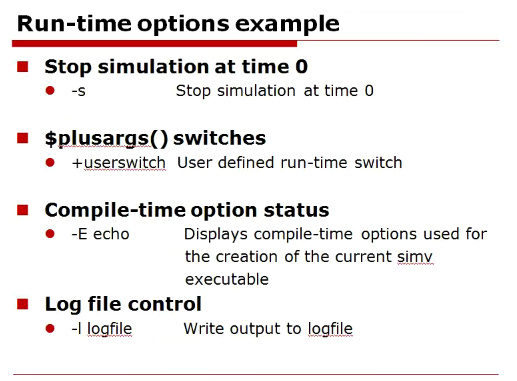

- -R -- 表示生成simv文件后自动执行

- -gui -- 表示产生DVE图形界面

- -l -- 编译的时候产生的信息记录到后面的文件中

- -sverilog -- 支持system verilog

- +v2k -- 支持verilog 2001语法

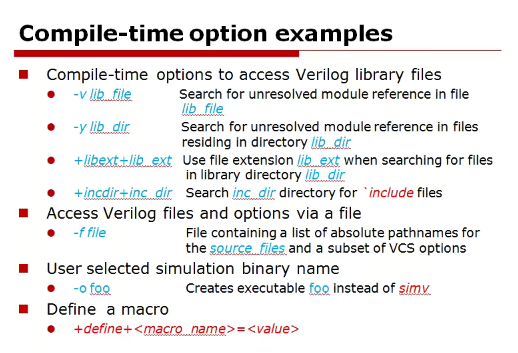

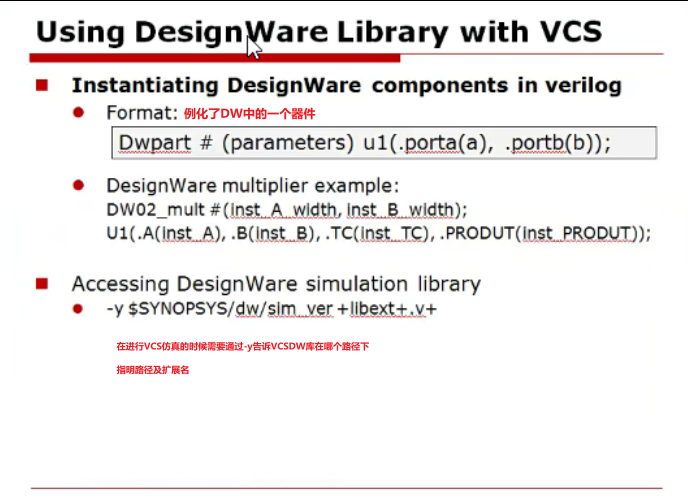

- -v lib_file -- -v 使用工艺库

- -y lib_dir -- 指定vcs寻找的路径

- +libext+lib_ext -- 在lib_dir路径中寻找文件的时候指明文件的后缀名

- +incdir+inc_dir -- 在rtl代码中使用`include的时候,指定include所指明文件所在的路径

- -f file -- 将很多源代码整合到一个filelist文件中去,通过-f调用

- -o foo -- 修改simv文件名称为foo

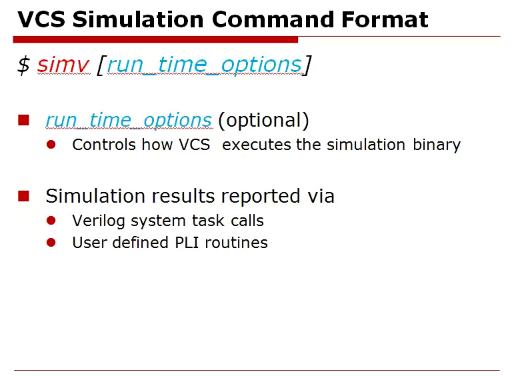

7.VCS仿真命令

- -l logfile 记录仿真文件

8.库文件使用

9.回顾

- -Mupdate -- 增量编译

- -l compile.log -- 生成compile.log文件