数字IC设计全流程设计

- 掌握数字集成电路设计的流程

- 数字设计流程中每个阶段主要做哪些工作?

- 数字设计流程中每个阶段使用的主要EDA工具?

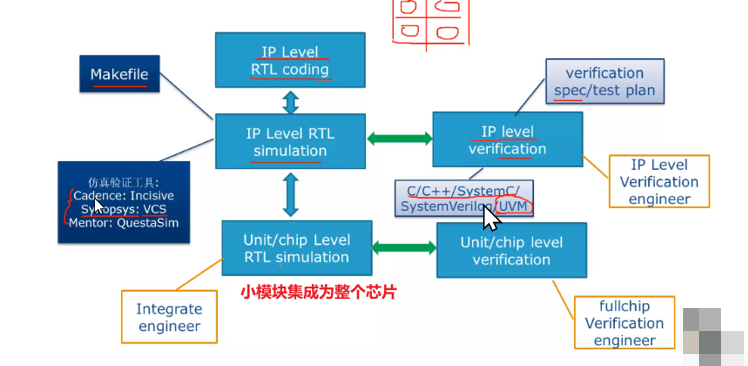

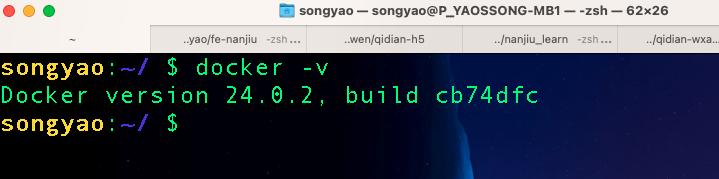

数字电路常用软件公司Mentor(questasim),Synopsys(VCS),Candence(incisive)

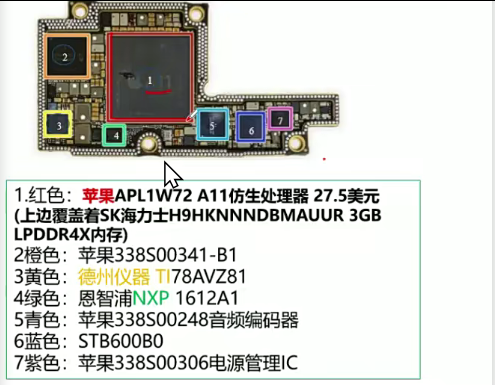

1.手机芯片简介

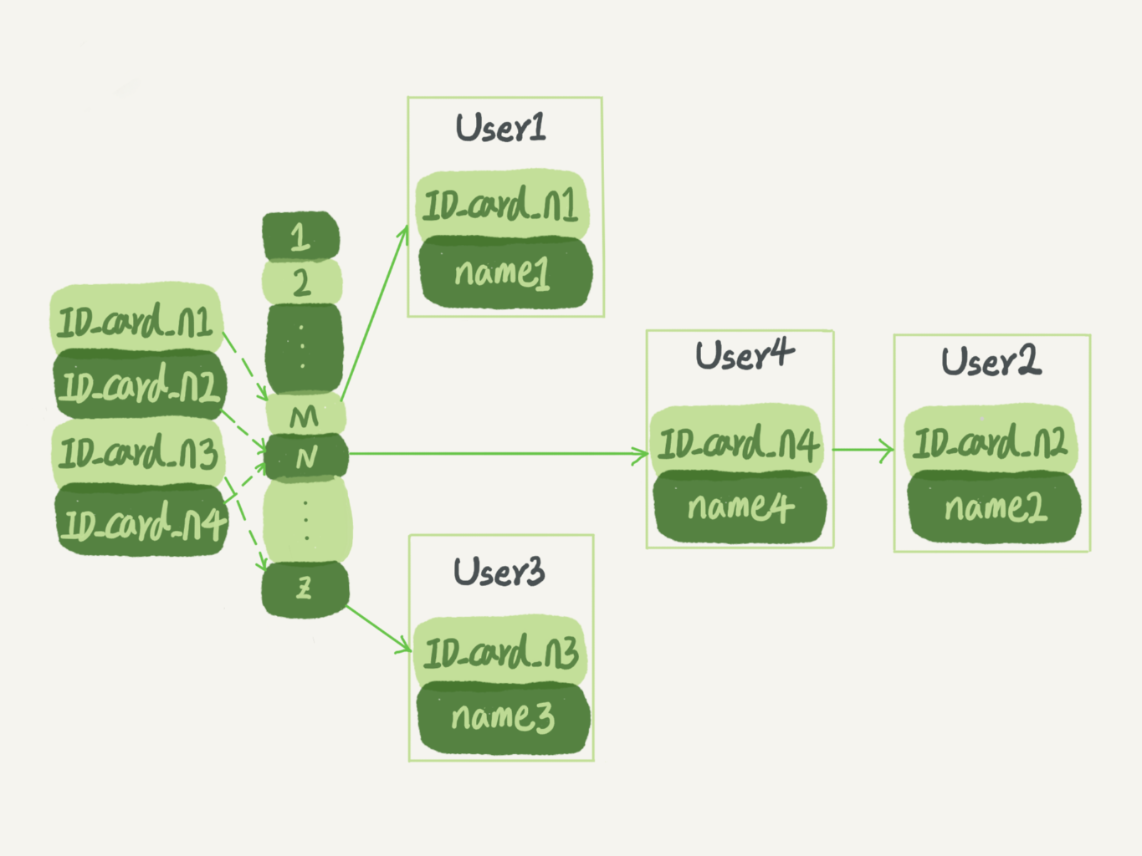

- 电子设备中集成了很多的芯片,通常由不同的厂商进行提供

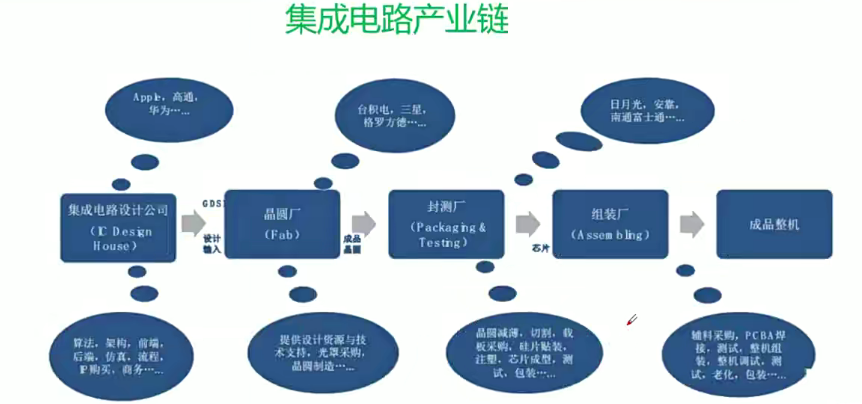

2.集成电路产业链

- design house:进行芯片设计,算法,架构,前端,后端,仿真,,,,

- Fab:晶圆厂,提供设计资源与技术支持

- Packaging:封测厂,晶圆厂和封测厂临近

- Assembing:组装厂

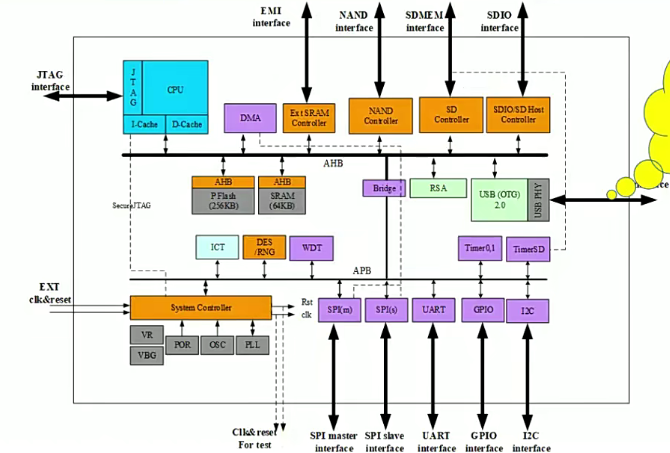

3常见SoC架构图

- system on chip

- CPU(ARM,X86) -- 整个系统的核心

- AHB,APB -- 进行各个模块之间的通信,上面可以外挂很多模块;快速设备挂载在AHB上(内存),慢速设备挂载在APB总线上

3.1 SoC中IP的功能

3.2 芯片功能

- SDC -- SD controller

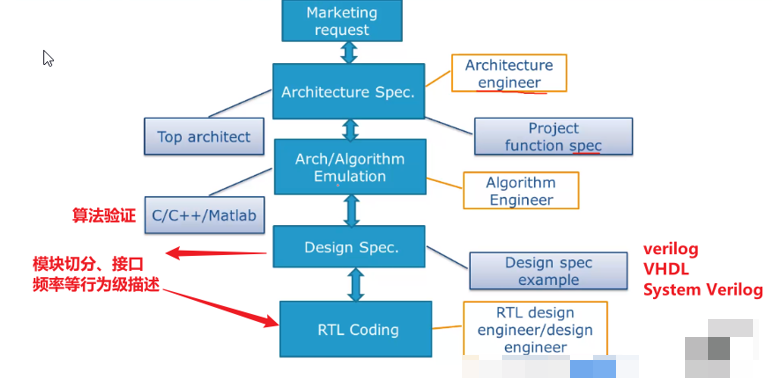

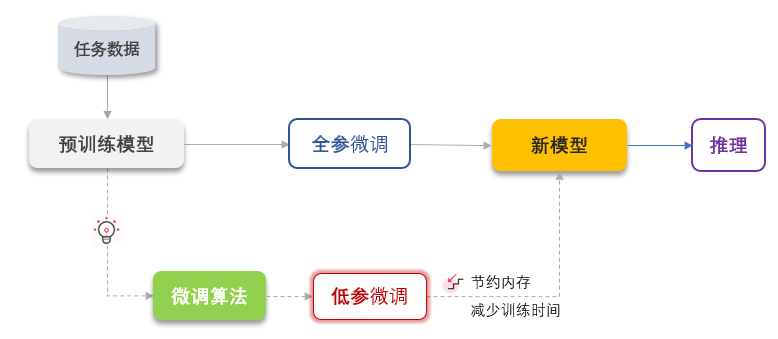

4.数字IC设计流程

- 指标:频率,内存

- 制定芯片的具体目标:市场人员到市场上进行调研,今年会生产什么样的Soc,使用的架构是什么,关于DDR4或者是DDR5、USB2.0、USB3.0等。

- 系统级设计:C语言或者是Matlab进行算法的仿真。对于成熟的模块是不需要进行算法建模的。

- 前端设计:RTL设计、RTL仿真、硬件原型验证(FPGA)、电路综合。

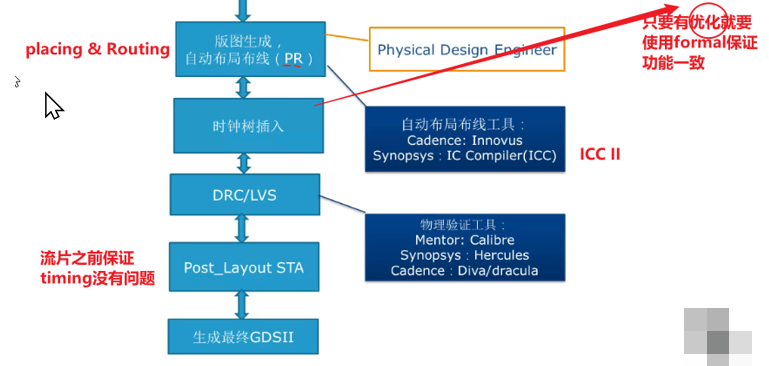

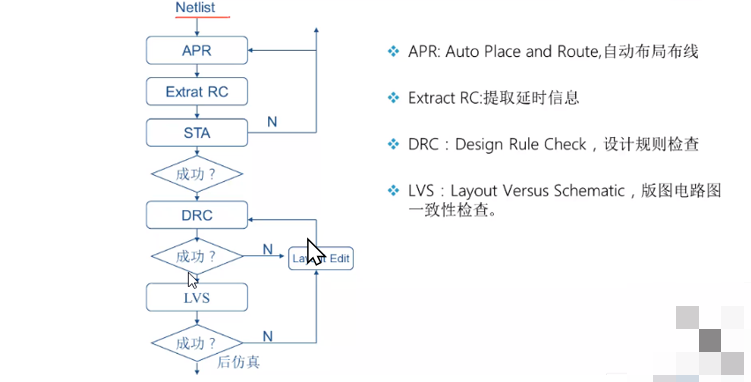

- 后端设计:版图设计、物理验证、后仿真等;后端设计会进行布局布线(PR)。

- RTL:寄存器传输级的硬件描述语言。在硬件描述语言中所描述的电路,都是由Gate进行设计出来的,所以需要进行逻辑综合,将RTL转化为电路,进行验证。

5.数字IC设计具体指标

- PPAF--Performance,Power,Area,Function

- 工艺:28nm,14nm,10nm

- 制作工艺决定性能,新工艺往往使用在手机和电脑的CPU

- die面积越小,成本越低,按wafer进行计算

- 封装受到pin数量的影响,需要考虑散热问题

- 接口用于不同module之间的交互

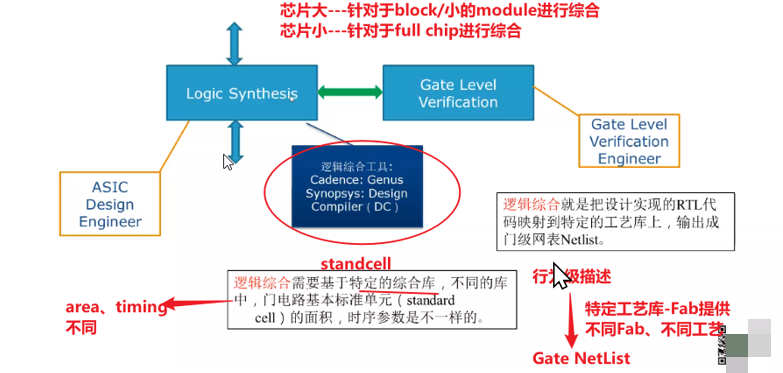

6.基于Standcell的Asic的设计流程

- StandCell -- 标准库单元

- RTL -- 寄存器传输级硬件描述语言

- System Verilog进行设计和验证

- 电路版图--基于Netlist进行布局布线

PR阶段:会固定放置standcell,固定的时候会考虑时序(standcell放置的越远,delay越大)、物理空间等。

7.Digital IC design flow

Design Spec-设计规格说明书

C/C++进行设计reference model

验证更多的是行为级的描述

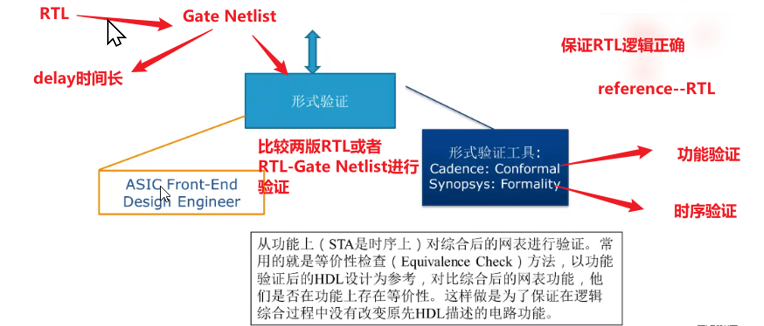

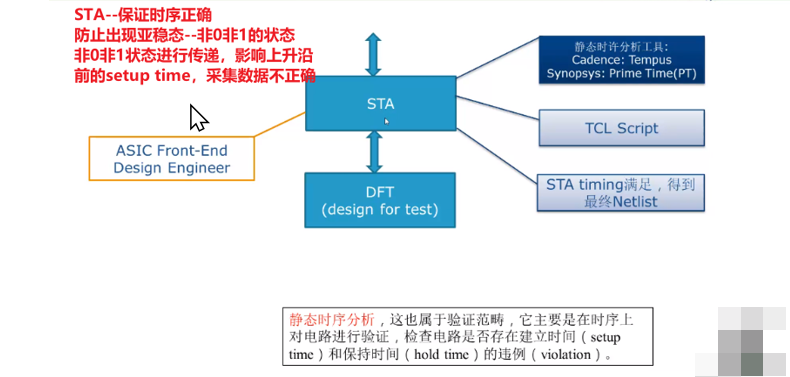

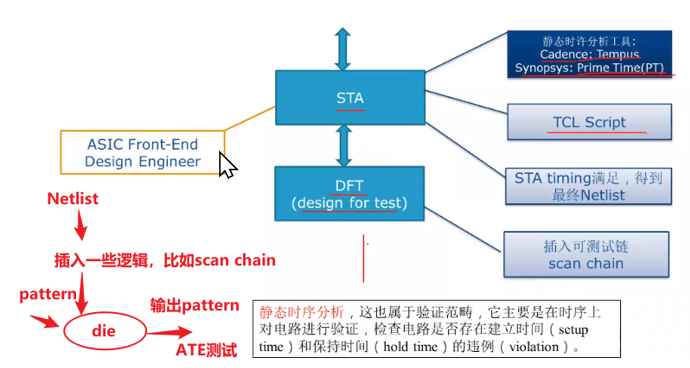

前期是根据design spec进行coding,仿真验证都是根据RTL进行Verification;RTL进行Sysnthesis之后得到的是Gate Level NetList,需要对Gate Level Netlist进行仿真,时间比较长。进行形式验证,形式验证是为了保证逻辑正确,简单理解就会使输入0,输出1,是否正确。

设计过程中可以保证逻辑和function是正确的。在实际进行流片的时候,由于工艺原因导致芯片内部出现一些问题。为了避免这些问题,在拿到裸片之后,可以进行测试。

8.前端设计(RTL to Netlist)

9.后端设计(Netlist to Layout)

10.VLSI设计

![原来你是这样的JAVA–[07]聊聊Integer和BigDecimal](https://img2024.cnblogs.com/blog/37001/202402/37001-20240224171021931-593439949.png)