1 导读

MIG 是xilinx的memory控制器,功能强大,接口易用。当硬件设计在设计对应的DDR接口时,最好先用MIG去配置一遍DDR的管脚约束、电平约束,从而避免硬件设计好了,实际却无法使用的情况。

需要注意的地方如下:

2 DDR型号

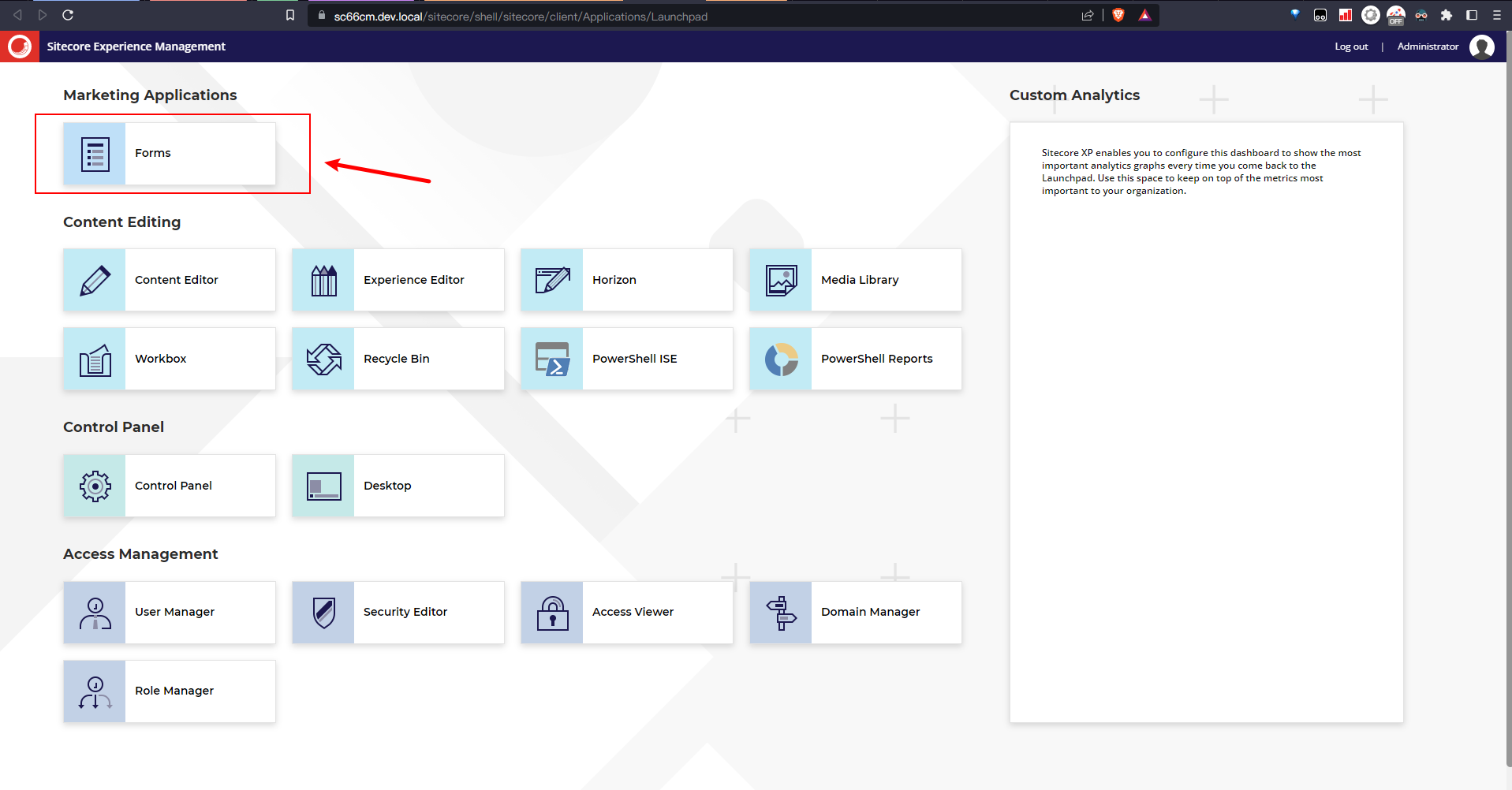

根据需求,选定所需的MIG型号

图 2‑1 选择对应的DDR3型号

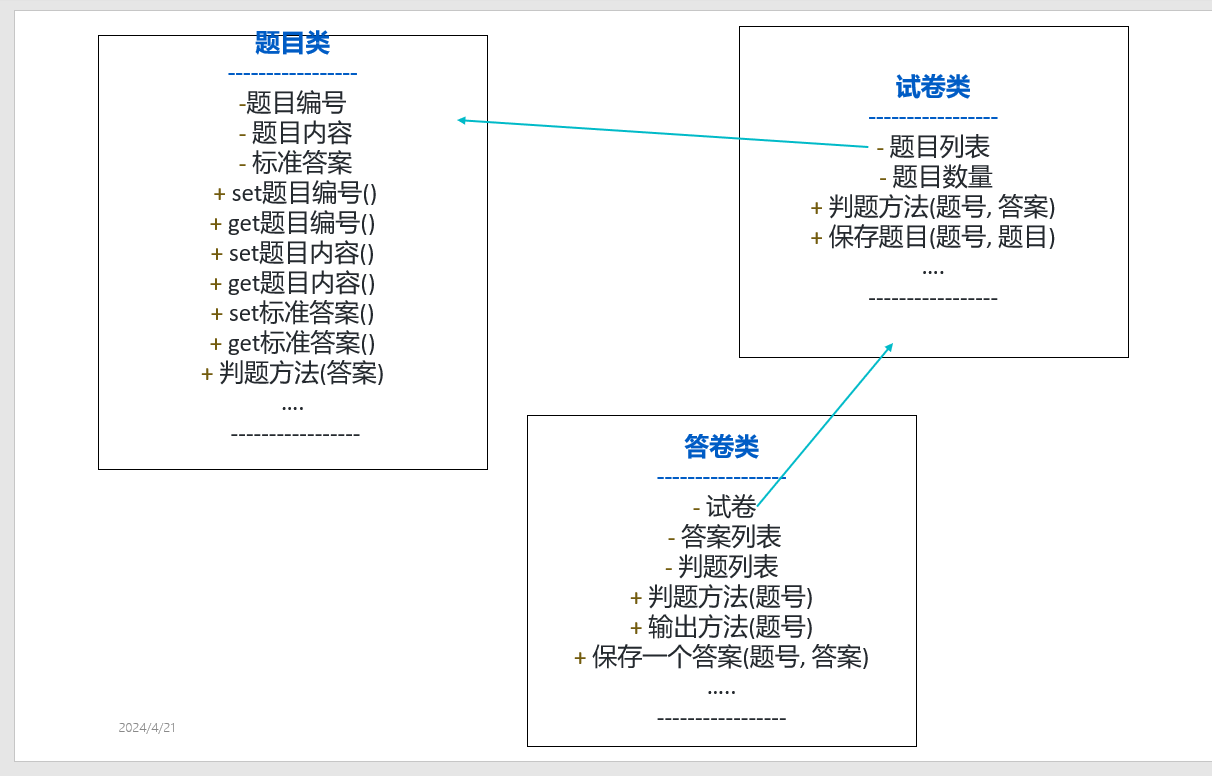

图 2‑2 不同型号、电平、FPGA速度等级对应的最高速率

3 电平标准

几个个位置的电平需要注意:

3.1 Memory Voltage

有1.35V和1.5V可选,有什么区别呢?简单来说,1.35V对应的PHY速率会低于1.5V,涉及到DDR的读写速度,不过1.35V显然在功耗上更有优势。

下面我们展开来看看

首先,Memory Voltage 分为1.5V和1.35V的差别,分别对应的是DDR3和DDR3L,下面的描述来自网络,可以看出DDR3L更多用在消费电子产品上,DDR3更多用在工业产品上。

• DDR3L is a special type of DDR3 where L refers to low voltage standard.

• DDR3 needs a voltage of 1.5V while DDR3L needs only 1.35V.

• DDR3L consumes less power than DDR3.

• DDR3L generates less heat when compared to DDR3.

• DDR3L is mostly used in mobile devices such as laptops and embedded devices while DDR3 is mostly used in personal computers. However, the re are mobile devices, which use DDR3 as well.

• The market price of a DDR3L module is higher than the market price of a DDR3 module.

3.2 Vccaux_io

有1.8V和2.0V可选,简单来说,1.8V对应的PHY最大速率低于2.0V

先看看这个电源是干嘛的,VCCAUX_IO只适用于HP BANK,专门为高速单端信号传输准备的

下面这段话又做了补充,1.8V/2.0V的电平目的是为了作为predriver增加信号的驱动能力。

3.3 VRN/VRP

VRN and VRP are used for the digitally controlled impedance (DCI) reference for banks that support DCI

这2个信号是用来控制数字可控阻抗的,每个HP BANK都有,如果是能了级联模式,可以只在其中一个BANK上接对应电平,其它BANK 在FPGA内部级联过来。不过这个操作需要手动修改一下约束,指定哪个BANK是MASTER,哪个BANK 是被级联的SLAVE。

一般设计时,会把地址线所在的bank作为MASTER,数据线所在的BANK作为SLAVE,降低走线密度。当然如果只有一个BANK,那就必须连接。

3.4 VREF

如果要DDR稳定工作在较高速率下,必须将该电压连连接到memory voltage的一半,从而保证不受到较大电源噪声的影响。一般在数据对应的BANK需要连接该电平。

实际产生VREF都有专用的IC解决方案,找一个xilinx对应的评估板,这部分抄过来用就可以。

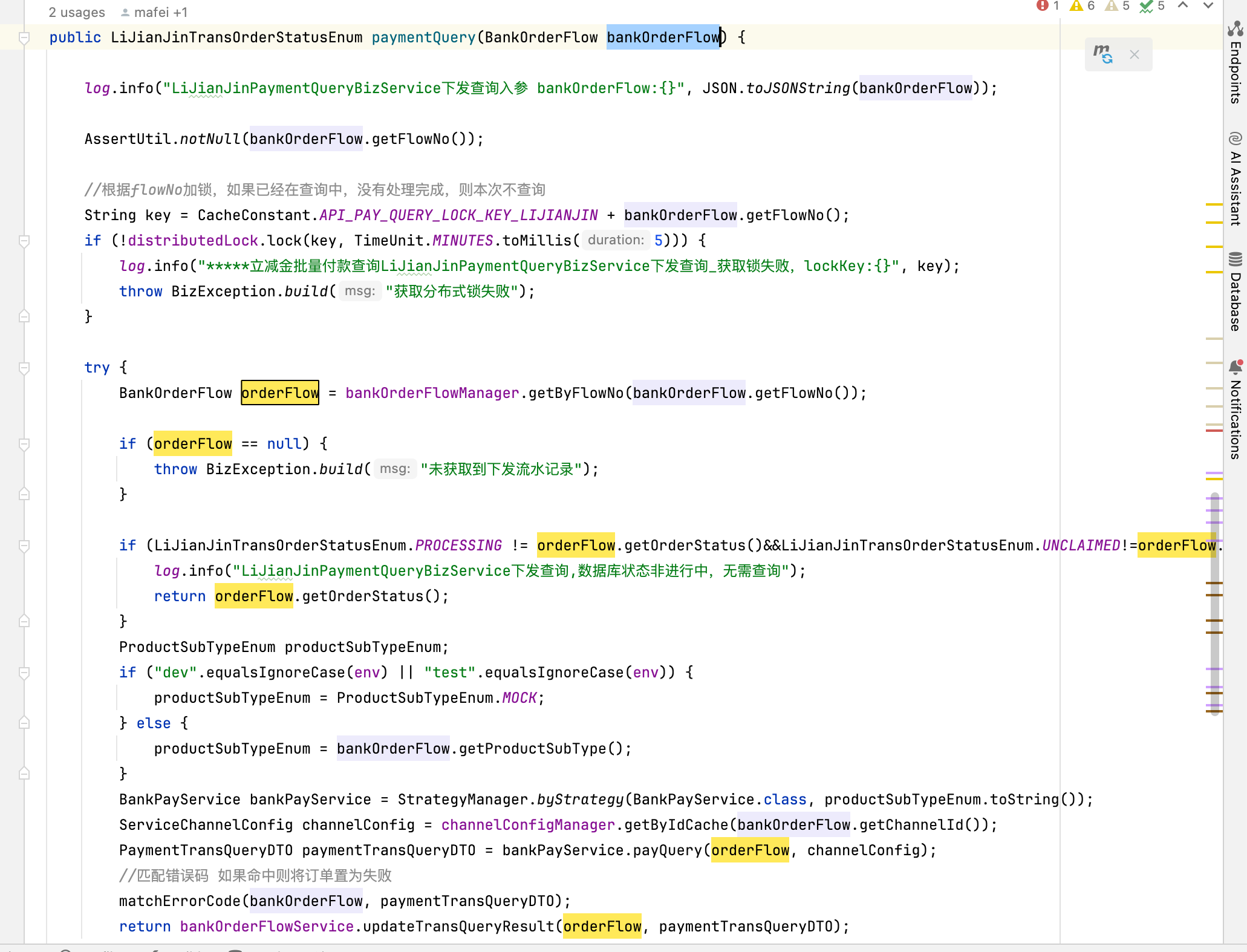

图 3‑1 KC705 DDR电源方案

4 管脚约束

DDR的管脚约束实际上是很有讲究的,在开始硬件设计之前必须查阅手册、参考设计,然后使用MIG进行验证之后再开始硬件设计。

1、 要想得到最高速率,DDR3需要连接到HP BANK

2、 DDR3对应的HP BANK必须是连续的,中间不能有间隔。

![[Lua][Love Engine] 打砖块游戏实现过程与知识点](https://xiaonenglife.oss-cn-hangzhou.aliyuncs.com/static/pic/2023/08/20230821054725_image-20230821054659181.png)