1.1 先来看看信号线的描述

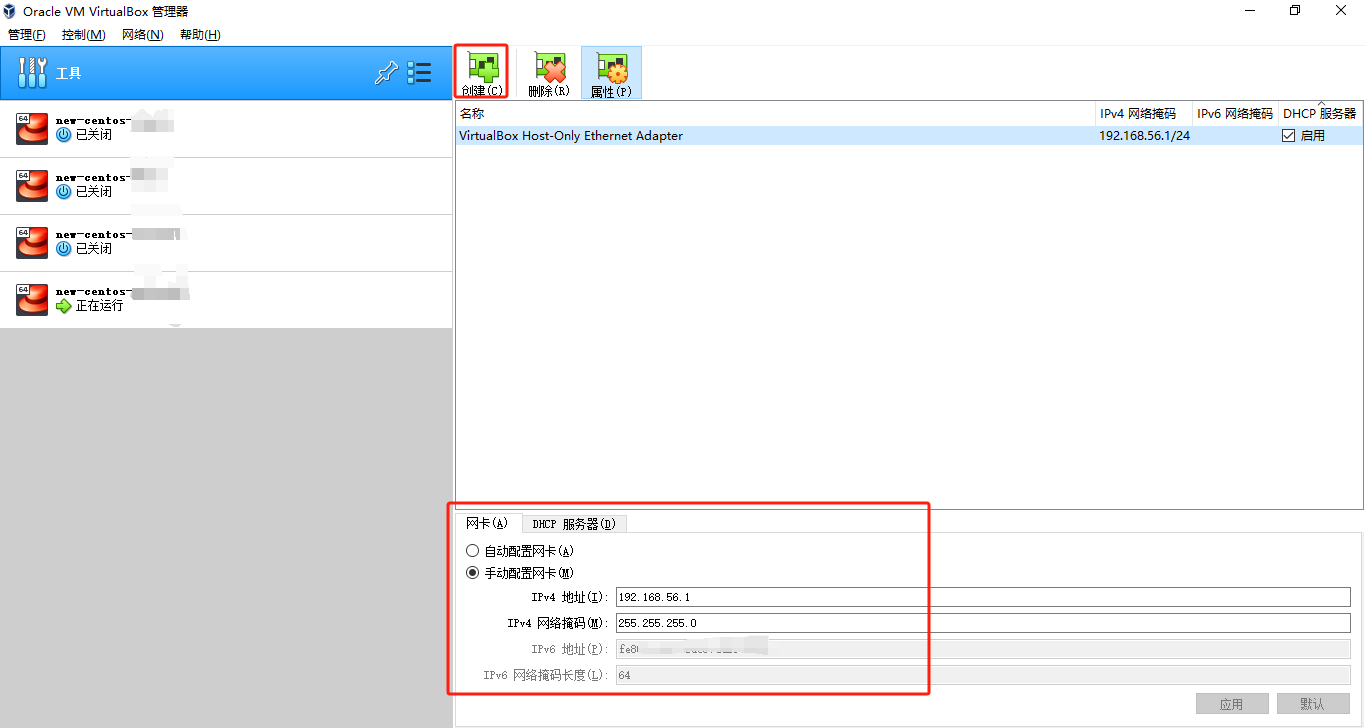

我们以X16的器件为例,下面的截图来自 镁光的官方手册 https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr3/4gb_ddr3l.pdf?rev=8d4b345161424b60bbe4886434cbccf4

2.1 DDR如何实现读写操作

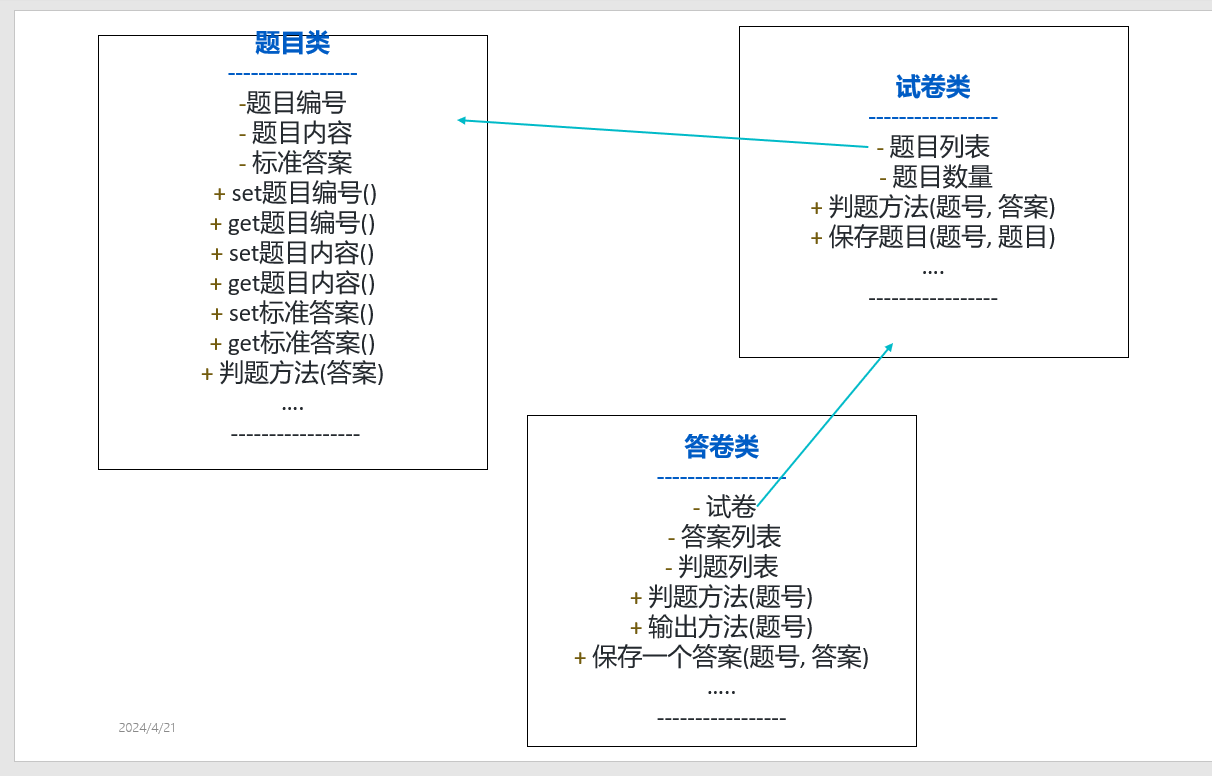

下面再来一张X16的器件内部框图,下面的解释也都是适用于X16器件。

框图可以看出,行地址和列地址是复用的,通过RAS与CAS信号实现复用,这样实际地址线就有RA[14:0]、CA[9:0]、 BA[2:0] 共15+10+3 = 28 bit,对应256M地址,1个地址对应16bit数据,因此共512MB容量。

这里会有同学问了,1个地址对应16bit数据,那么是不是意味着单次必须写入16bit的整数倍,且offset地址必须是16bit整数倍呢?不是的,原因是DDR按照8bit作为1个Byte Lane,使用DM()信号表征对应的Byte是否有效,从而允许写入奇数字节的offset地址和数据长度。

典型的,如果要向0x1地址写入1字节数据,那么DDR会认为此时地址为0x0,UDM此时有效,LDM此时无效,从而向0x1 地址写入了1字节长度的数据。

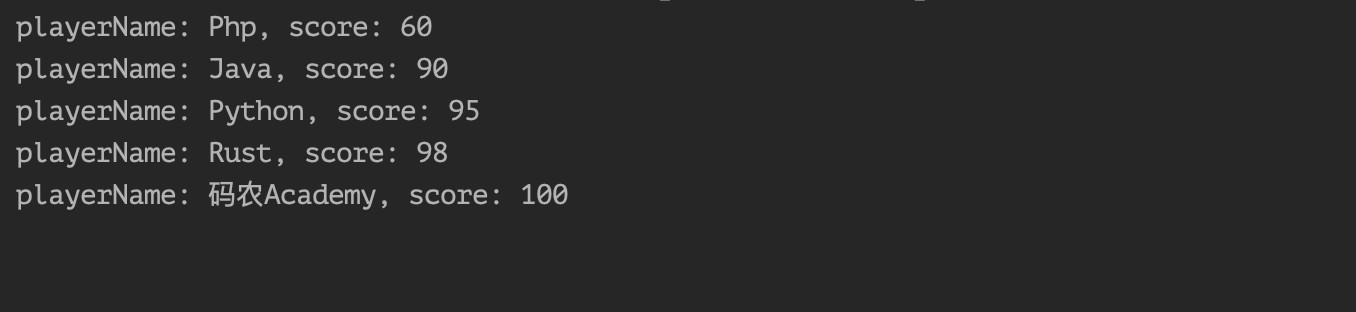

典型的,如何最大化DDR写入读出的速度呢?如果每次写入读出都要先传递1次地址,那可就效率太低了,DDR需要支持burst的传输,即先写入地址,然后联系写入burst长度的数据。那么burst的长度是多少,如何指定呢?

下图是xilinx MIG配置页面,可以看到只支持burst length 8,就对应 8*16bit/8bit = 16字节

是MIG通过向DDR写入MODE REGISTER指定的。

BURST LENGTH为8,这个意思就是如果单次传输地址、长度向16字节对齐,就可以得到最大效率。因为避免了频繁写入地址的操作。

至于写入、读出的时序细节,建议参考镁光的器件手册。

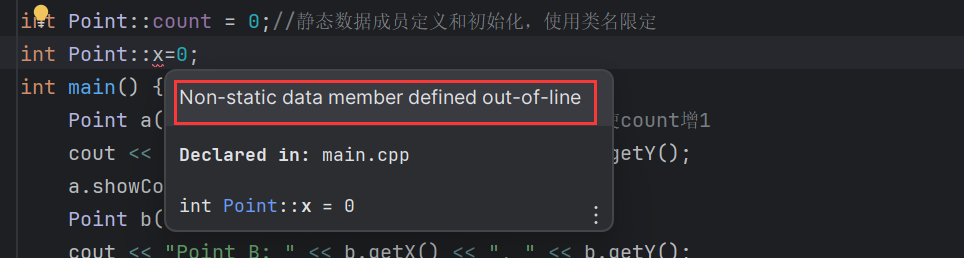

3.1 如果只需要用到X16的低8bit,怎么办

有时候处于兼容性等考虑,对于1个x16数据位宽的器件,只需要用到其低8bit数据位宽,这时候应该如何处理呢?

1、 根据器件的原理,如果你只用低8bit,那么会损失掉一半的地址空间;

2、 在对mig进行配置时,必须自定义器件,而不能随意更换器件型号或者直接忽略高8bit,这会导致初始化和校准无法完成。

硬件设计上需要注意哪些呢?下面是官方给的建议,建议按照要求设计。