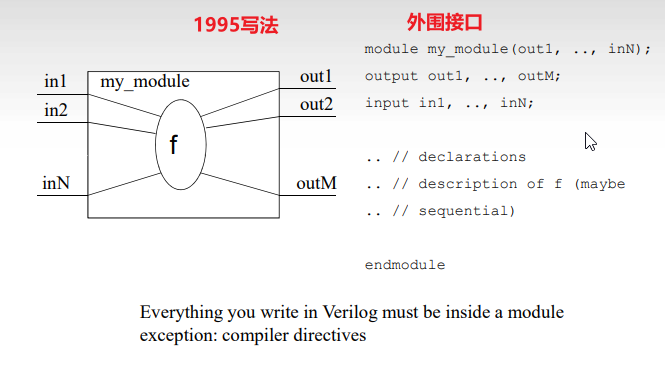

Module

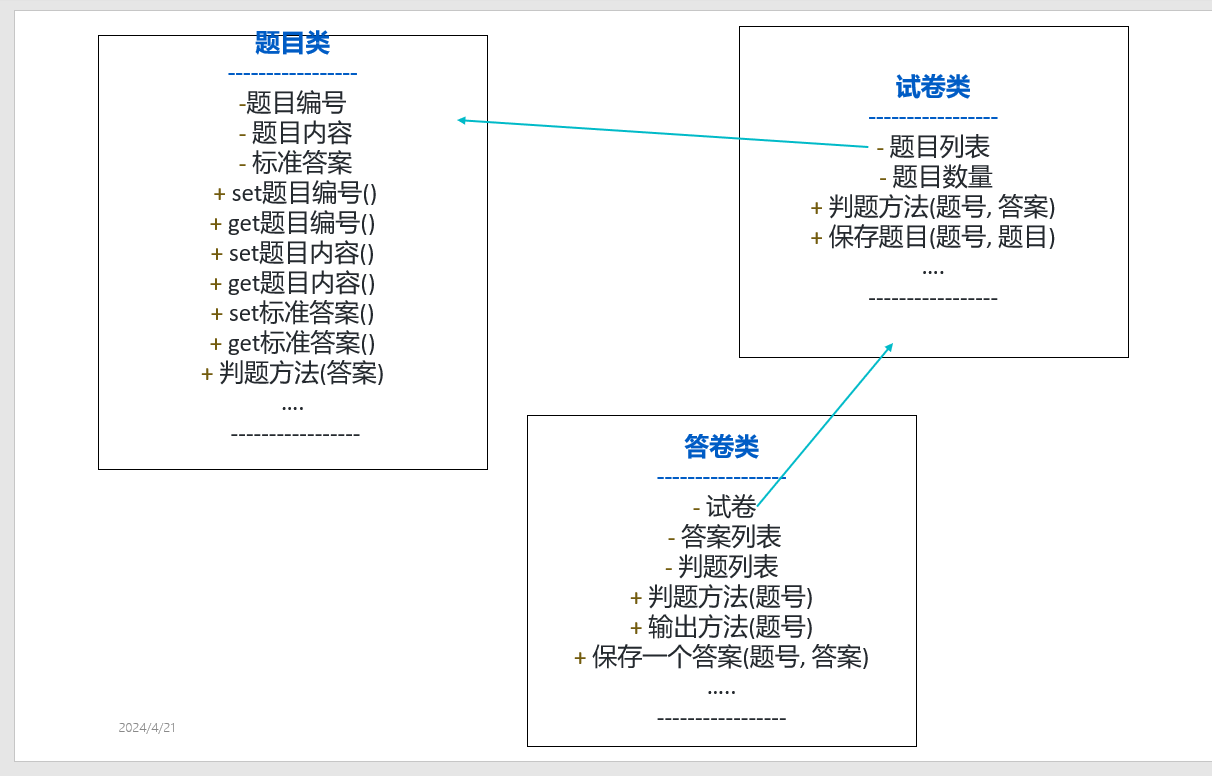

Module是verilog中的关键字,是对电路建模的最小单元。verilog中构建一个电路,对于一个硬件进行描述在module中进行。

半加器

module half_adder(S,C,A,B);

output S,C;

input A,B;

wire S,C,A,B;

assign S = A ^ B;

assign C = A & B;

endmodule

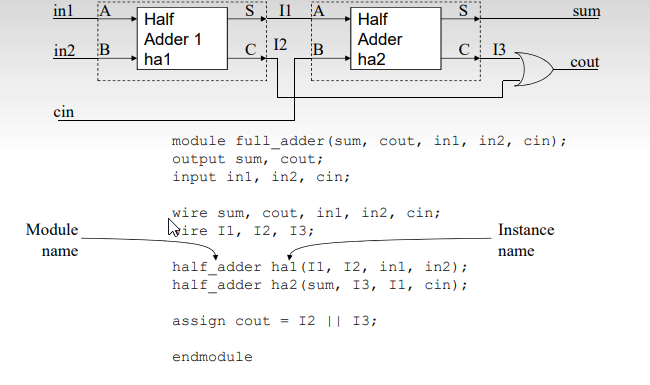

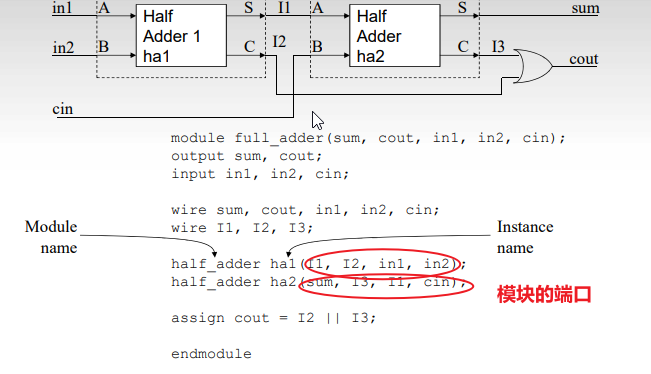

全加器

module full_adder(sum,cout,in1,in2,cin);

output sum,cout;

input in1,in2,in3;

wire sum,cout,in1,in2,cin;

half_adder ha1(I1,I2,in1,in2);

half_adder ha2(sum,I3,I1,cin);

assign cout = I2 || I3;

endmodule

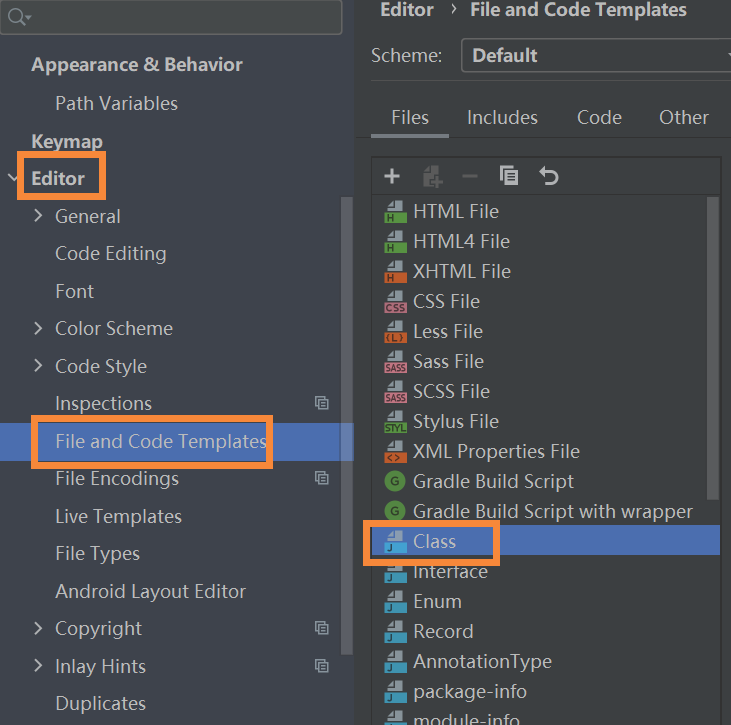

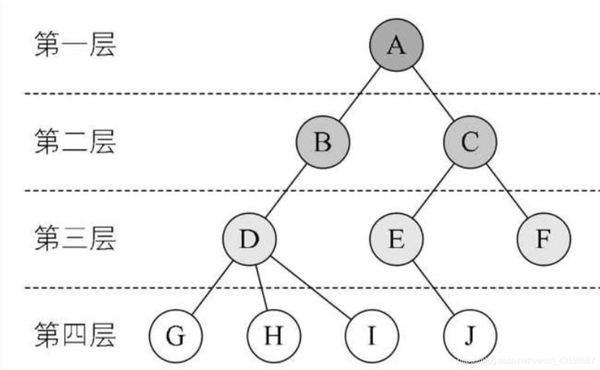

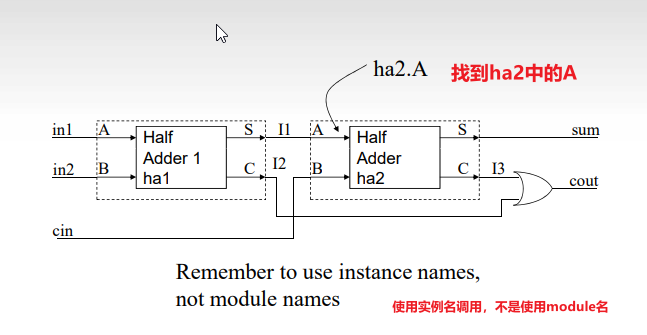

Hierachical Names

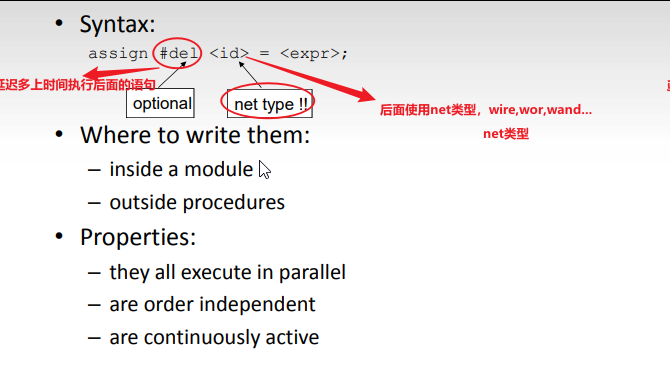

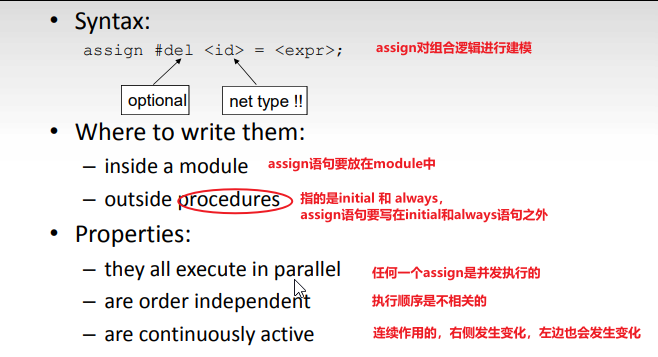

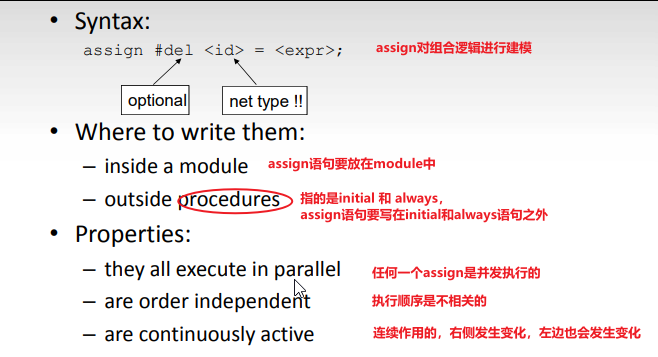

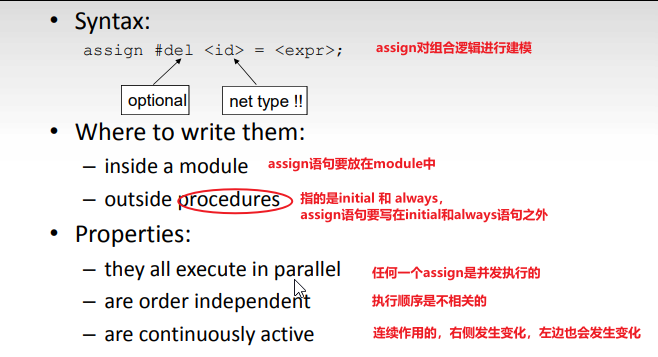

Continuous Assignments(连续赋值语句)

- 将左侧和右侧连起来,建立连接关系

- 线网类表示逻辑门与模块之间的连接,具体的类型有:wire、wand、wor、tri、triand、trior、tri0、tri1、trireg、uwire、supply0、supply1

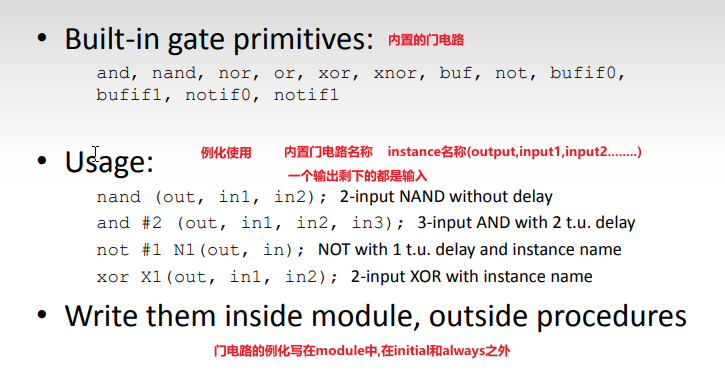

Structural Model(Gate Level)

- 组合逻辑电路是没有DFF的,触发器如何描述,取决于综合逻辑工具。

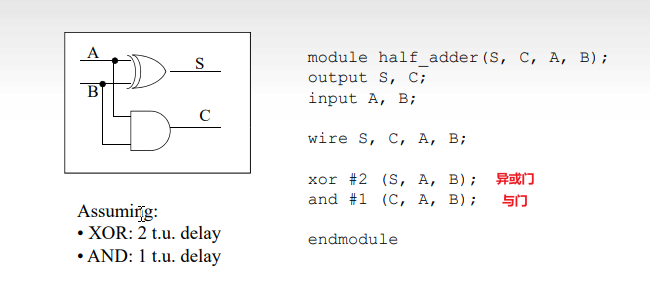

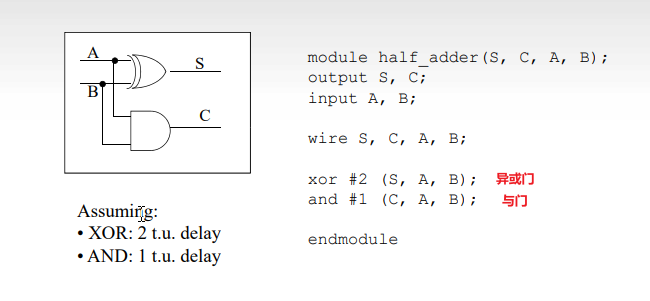

半加器的实现

- 使用verilog中的门电路实现半加器

module half_adder(S,C,A,B);

output S,C;

input A,B;

wire S,C,A,B;

xor #2 (S,A,B);

and #1 (C,A,B);

endmodule

- 这种门电路的实现是不推荐的,这里的门电路相当于将RTL代码进行逻辑综合之后映射到特定工艺库中的东西。

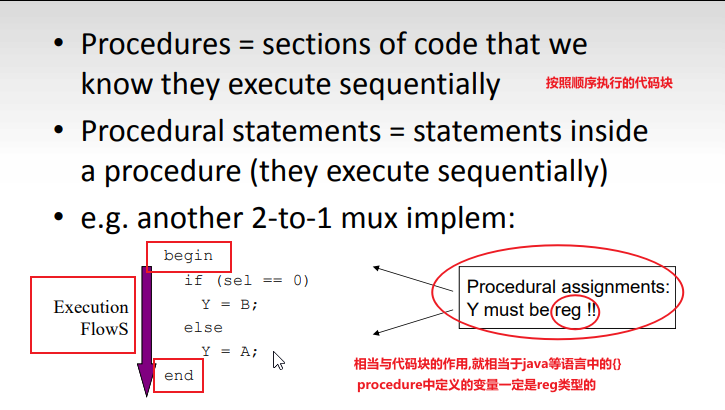

Behavioral Model-Procedure(i)

- 实现二选一的mux

begin

if(sel == 0)

Y = B;

else

Y = A;

end

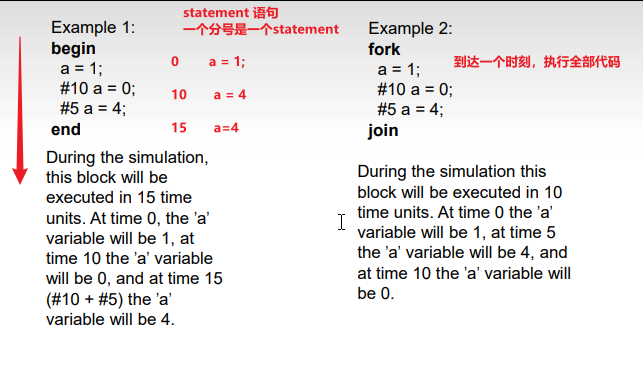

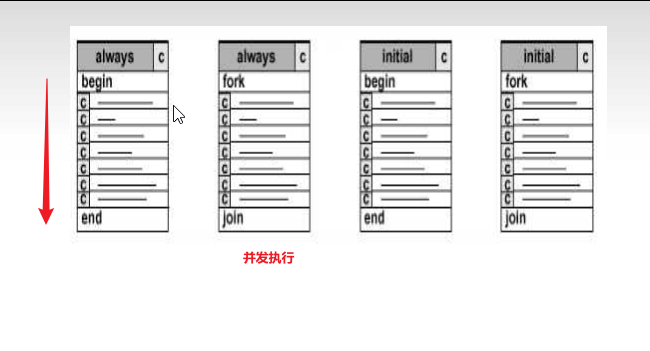

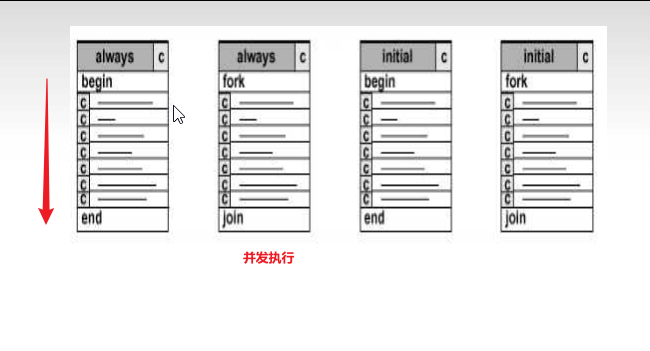

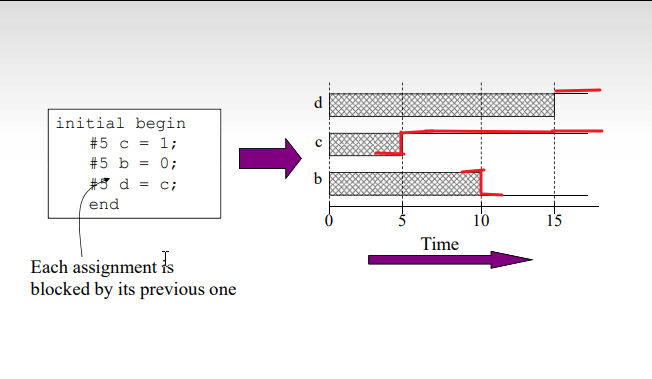

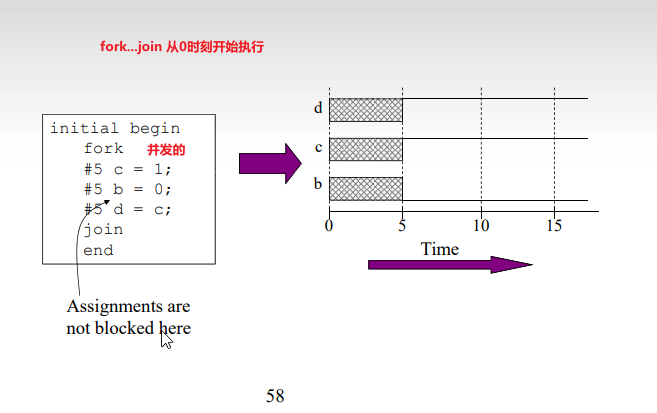

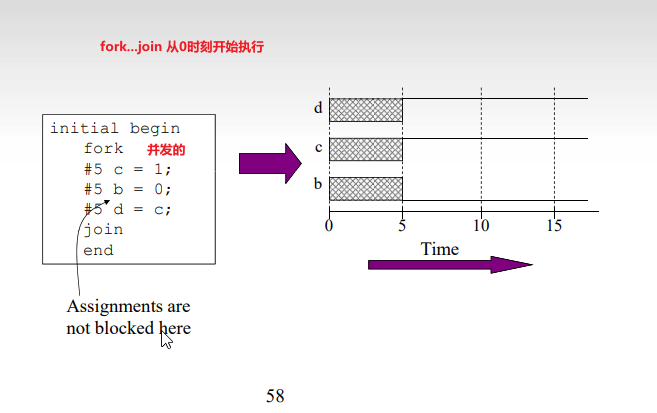

Block statement

- fork-join是不可综合的,不能用于构建电路

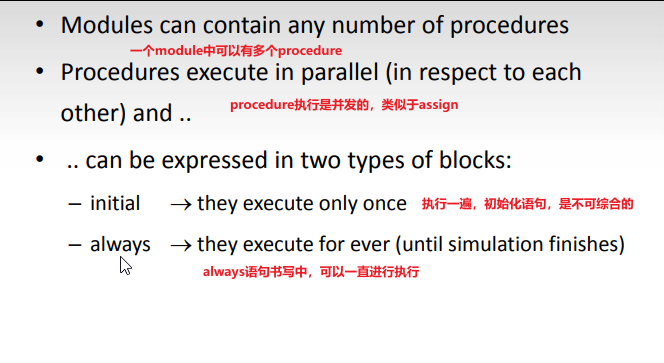

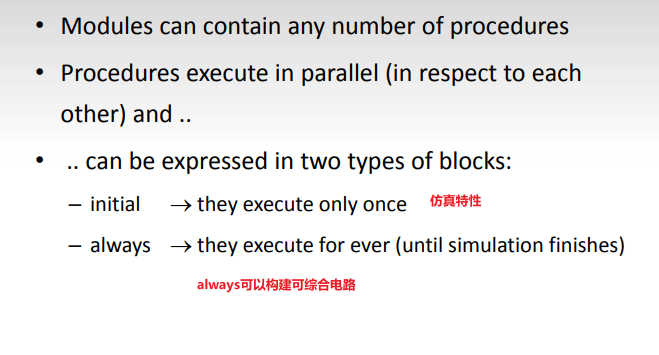

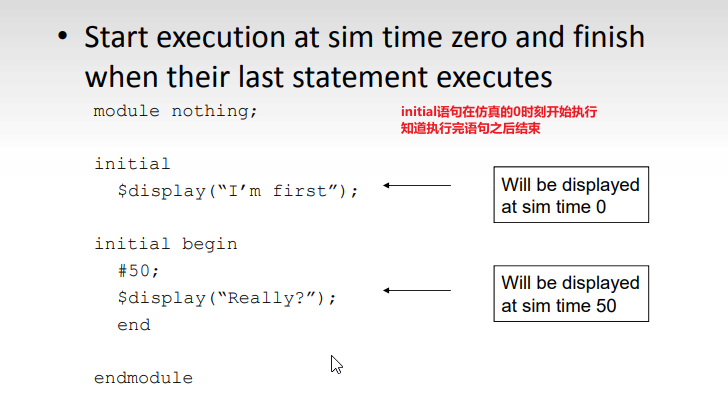

Initial & Always

- @--等的意思

event

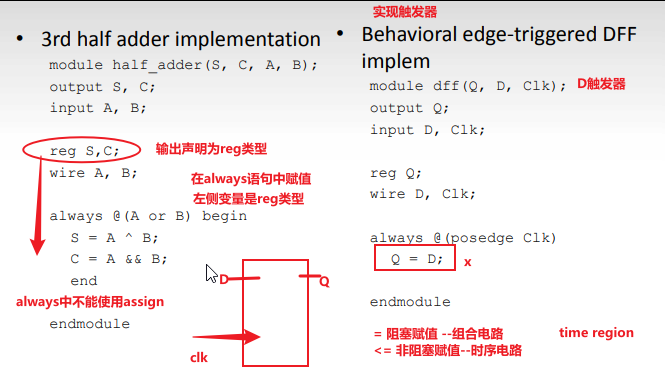

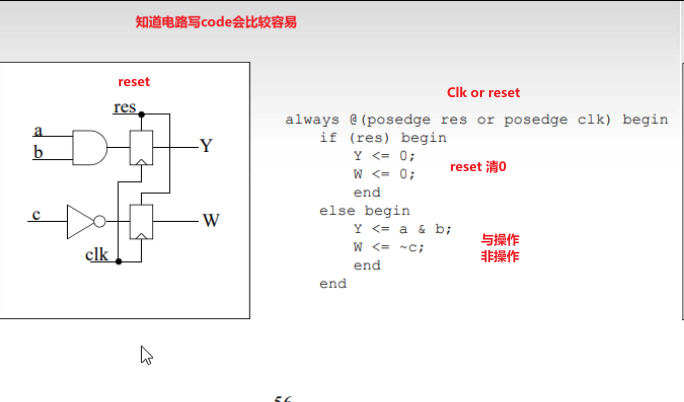

半加器实现--always语句

- 半加器和DFF

// half adder

module half_adder(S,C,A,B);

output S,C;

input A,B;

reg S,C;

always @(A or B){

S = A ^ B;

C = A && B;

}

endmodule

//DFF

module dff(Q,D,Clk);

output Q;

input D,Clk;

reg Q;

wire D,Clk;

always @(posedge Clk){

Q = D; //这里这种写法是错误的,应该使用非阻塞赋值写法

}

endmodule

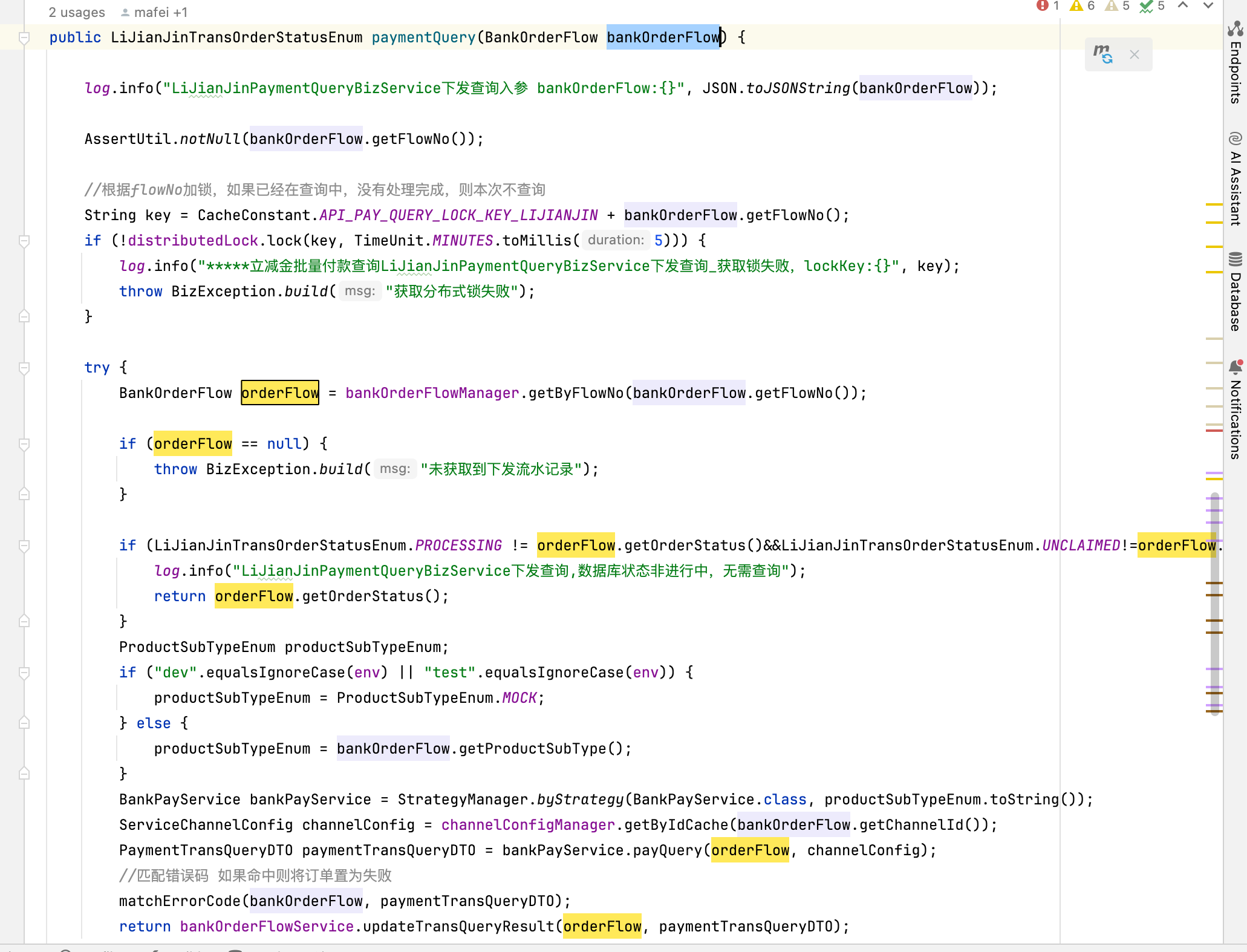

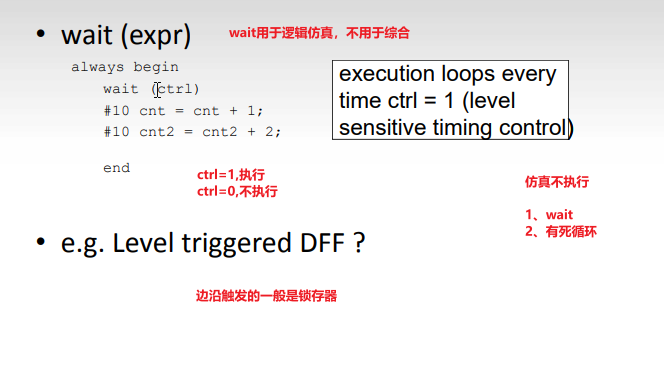

Timing

- verilog语言中特有的

if

四选一mux实现

// 4-to-1 mux

module mux 4_1(out,in,sel);

output out;

input [3:0] in;

input [1:0] sel;

reg out;

wire in,sel;

always @(in or sel)

if(sel == in[0])

out = in[0];

else if(sel == in[1]

out = in[1];

else if(sel == in[2]

out = in[2];

else

out = in[3];

endmodule

- 还可以使用三目运算符

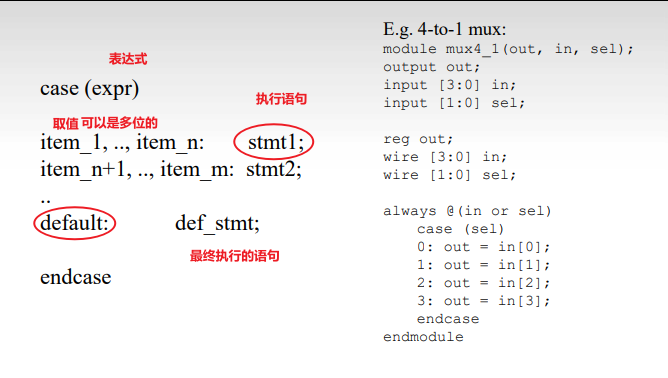

case

实现四选一

module mux 4_1(out,in,sel);

output out;

input [3:0] in;

input [1:0] sel;

reg out;

wire [3:0] in;

wire [1:0] sel;

always @(in or sel)

case (sel)

2'b00 : out = in[0];

2'b01 : out = in[1];

2'b10 : out = in[2];

2'b11 : out = in[3];

endcase

endmodule

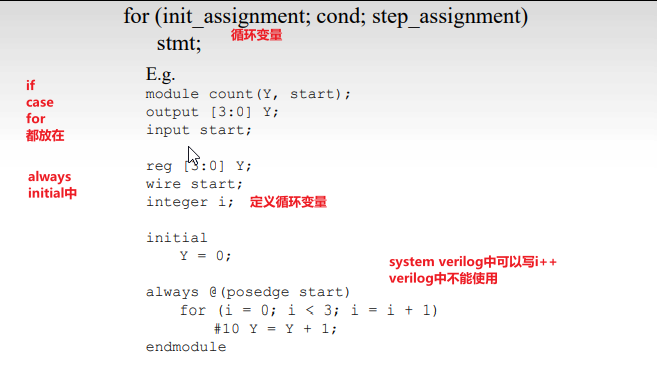

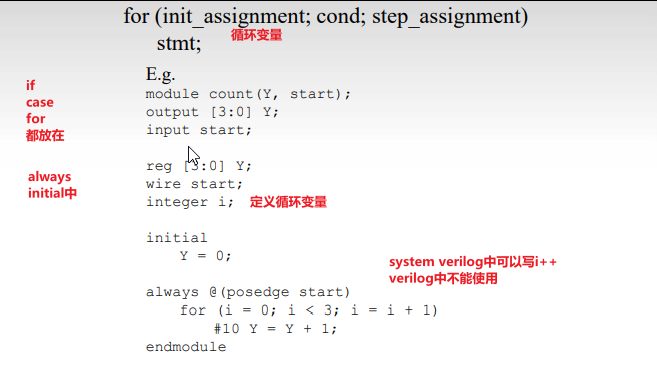

for

- 可以实现计数器

module count(Y,start);

output [3:0] Y;

input start;

reg [3:0] Y;

wire start;

integer i;

initial

Y = 0;

always @(posedge start)

for(i = 0;i < 3;i = i+1)

#10 Y = Y + 1

endmodule

- for循环是不是可综合的,取决于循环变量是不是固定的

while

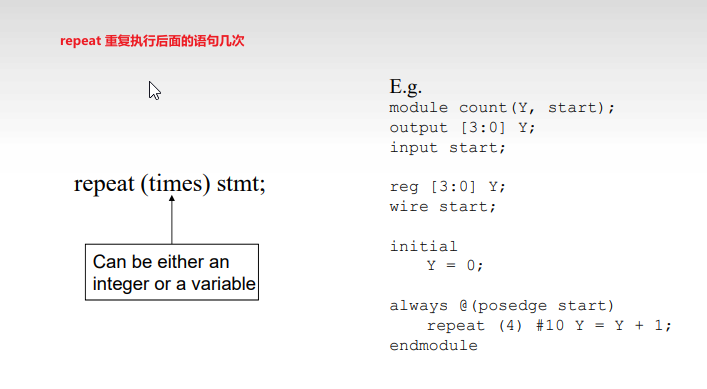

repeat

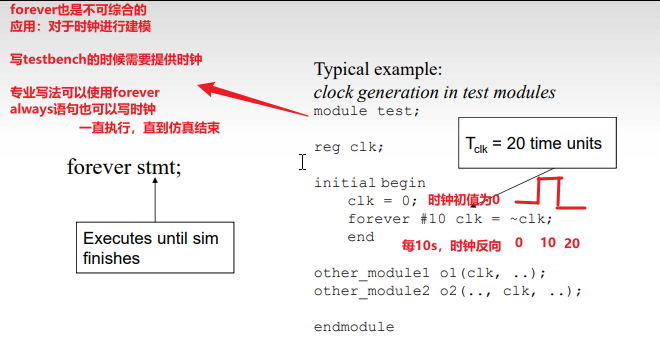

forever

- 时钟建模

module test;

reg Clk;

initial begin

clk = 0;

foever #10 clk = ~clk;

end

other_module o1(clk,....);

other_module o2(...,clk,...);

endmodule